# Impact of the Interfacial Layer on the Low-Frequency Noise (1/f) Behavior of MOSFETs With Advanced Gate Stacks

F. Crupi, P. Srinivasan, P. Magnone, E. Simoen, C. Pace, D. Misra, and C. Claeys, Senior Member, IEEE

Abstract—The impact of the interfacial layer thickness on the low-frequency (LF) noise (1/f noise) behavior of n- and p-channel MOSFETs with high- $\kappa$  gate dielectrics and metal gates is investigated. Decreasing the interfacial layer thickness from 0.8 to 0.4 nm affects the 1/f noise in two ways. 1) The mobility fluctuations mechanism becomes the main source of 1/f noise not only on pMOS devices, as usually observed, but also on nMOS devices. 2) A significant increase of the Hooge's parameter is observed for both types of MOSFETs. These experimental findings indicate that bringing the high- $\kappa$  layer closer to the Si-SiO<sub>2</sub> interface enhances the 1/f noise mainly due to mobility fluctuations.

Index Terms—High- $\kappa$  gate dielectrics, Hooge's parameter, interfacial layer, low-frequency (LF) noise, metal gates, mobility fluctuations.

#### I. INTRODUCTION

F-BASED high- $\kappa$  gate stacks have been proposed as substitutes for  $SiO_2$  to meet the challenges from the continued downscaling of CMOS devices [1]–[3]. Metal gates as a replacement for poly-Si are also being considered at the same time in order to eliminate polydepletion and resistivity effects, which arise from the use of poly-Si as a gate material. Moreover, channel mobility improvement and lower threshold voltage instability have been reported for the combination of  $HfO_2$  gate dielectrics with metal gates instead of poly-Si. The use of a thin interfacial layer (IL) of  $SiO_2$  or SiON in the high- $\kappa$  gate stacks has been found to be inevitable in order to provide better thermal stability and a lower density of interface defects with the Si substrate. Indeed, the peak mobility in n-channel MOSFET devices with  $HfO_2$  layers is observed to increase along with the thickness of the IL for both poly-Si and metal

Manuscript received May 8, 2006; revised June 1, 2006. The review of this letter was arranged by Editor C. Bulucea.

F. Crupi and C. Pace are with the Dipartimento di Elettronica, Informatica e Sistemistica, University of Calabria, 87036 Arcavacata di Rende (CS), Italy, and also with the Istituto per la Microelettronica e Microsistemi, Consiglio Nazionale delle Ricerche, 95121 Catania, Italy.

P. Srinivasan is with the Department of Electrical and Computer Engineering, New Jersey Institute of Technology (NJIT), Newark, NJ 07102-1982 USA, and also with the Interuniversity MicroElectronics Centre (IMEC), 3001 Leuven, Belgium.

- P. Magnone is with the Dipartimento di Elettronica, Informatica e Sistemistica, University of Calabria, 87036 Arcavacata di Rende (CS), Italy.

- E. Simoen is with IMEC, 3001 Leuven, Belgium.

- D. Misra is with the Department of Electrical and Computer Engineering, NJIT, Newark, NJ 07102-1982 USA.

- C. Claeys is with IMEC, 3001 Leuven, Belgium, and also with the Department of Electrical Engineering, Katholieke Universiteit Leuven, 3001 Leuven, Belgium.

Digital Object Identifier 10.1109/LED.2006.879028

gates [4], [5]. It has been shown that the Hf-related defects significantly enhance the low-frequency (LF) noise (1/f noise) of the gate and drain–current with respect to conventional  $SiO_2$  gate dielectrics [6]–[8].

We report here the impact of the IL on the LF drain–current noise of n- and p-channel MOSFETs with HfO $_2$ , using metal (TiN/TaN) as a gate material, in advanced gate stacks where the equivalent oxide thickness (EOT) is < 1.5 nm. The dominant 1/f noise mechanism is found to change from correlated number-mobility fluctuations [9]–[11] for EOT > 1 nm to mobility fluctuations [12] for EOT < 1 nm for nMOS devices. For pMOS devices, the major noise mechanism is found to be mobility fluctuations. Hooge's parameter [12] is used here as a figure of merit for comparison purposes. The differences observed here are mainly due to the influence of the nitrided SiO $_2$ -IL thickness variation on the 1/f noise.

## II. EXPERIMENTAL

The 1/f noise performance was investigated in n- and p-MOSFETs with gate width  $W=10~\mu\mathrm{m}$  and gate length L=1  $\mu$ m, with two different IL thicknesses—0.4 nm and 0.8 nm nitrided SiO<sub>2</sub> IL on top of which HfO<sub>2</sub> was deposited. The EOT of the studied n-MOSFETs is 0.92 nm (0.4 nm IL) and 1.44 nm (0.8 nm IL), respectively. The EOT of the studied p-MOSFETs is 1.31 nm (0.4 nm IL) and 1.35 nm (0.8 nm IL), respectively. Deposition of the high- $\kappa$  oxides was achieved either by atomic layer deposition (ALD) or by metal-organic chemical vapor deposition (MOCVD). Physical vapor deposited (PVD) TiN/TaN was employed as metal gate. These devices were annealed in ammonia at 800 °C for 60 s. On-wafer noise measurements were concurrently performed in Italy by using a purposely designed low-noise measurement system [6] and in Belgium by using the BTA9812 system in combination with the NoisePro software from Cadence. The 1/f noise has been evaluated in MOSFETs biased in linear operation with a drain voltage  $|V_{\rm DS}| \leq 50$  mV. For each bias point, we check that the gate leakage was at least one decade lower with respect to the channel current.

#### III. RESULTS AND DISCUSSION

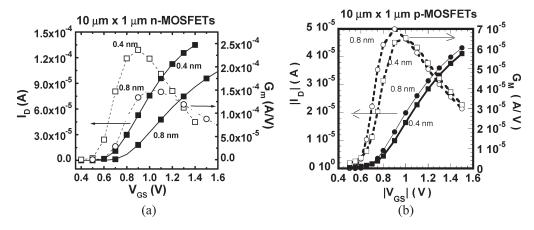

Fig. 1 shows the  $I_{\rm D}-V_{\rm G}$  and  $G_{\rm M}-V_{\rm G}$  characteristics of n- and p-MOSFETs. For n-MOSFETs, a higher value of  $I_{\rm D}$  and  $G_{\rm M}$  is observed for lower IL thickness, mainly due to lower

Fig. 1. Drain-current and transconductance versus gate voltage with  $V_{\rm DS}=50~{\rm mV}$  for different IL thickness of (a) n-MOSFET and (b) p-MOSFET.

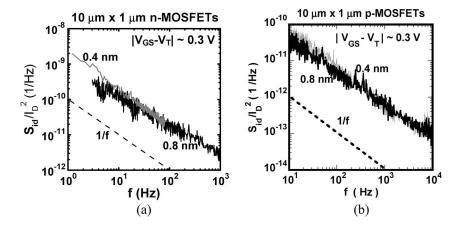

Fig. 2. Normalized drain-current spectral density for two different IL thicknesses studied for (a) n-MOSFET and (b) p-MOSFET. Note that the different frequency ranges are due to different measurement amplifier bandwidths since we used two different measurement systems as explained in the experimental section.

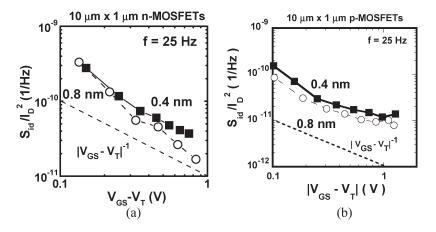

Fig. 3. Normalized drain-current noise spectral density versus gate voltage overdrive for two different IL thicknesses for (a) n-MOSFET and (b) p-MOSFET.

EOT values, whereas for p-MOSFETs, similar values of  $I_{\rm D}$  and  $G_{\rm M}$  are observed due to similar EOT values.

As seen in Fig. 2, the normalized 1/f noise spectra  $S_{\rm id}/I_{\rm D}^2$  of n- and p-MOSFETs for a gate voltage overdrive  $|V_{\rm GS}-V_{\rm T}|$  of 0.3 V are predominantly of  $1/{\rm f}^{\gamma}$  type, with  $\gamma\sim 1$ . A value of  $\gamma$  close to 1 has been observed also for other values of  $|V_{\rm GS}-V_{\rm T}|$  (not shown). Similar values of  $S_{\rm id}/I_{\rm D}^2$  are observed for different IL thicknesses at the same gate voltage overdrive in both types of devices.

Fig. 3 shows the normalized noise current spectral density  $S_{\rm id}/I_{\rm D}^2$  dependence over the gate voltage overdrive  $|V_{\rm GS}-V_{\rm T}|$  at f=25 Hz. Different dominant 1/f noise mechanisms between the n- and the p-type devices are noticed. For n-MOSFETs, the normalized  $S_{\rm id}$  varies as  $(V_{\rm GS}-V_{\rm T})^{\rm -m}$  with  $m\sim 1.5$  for the 0.8 nm IL thickness, which highlights that noise is due to correlated number-mobility fluctuations [9]–[11], and  $m\sim 1$  for 0.4 nm, which points out that noise is mainly due to mobility fluctuations. For p-MOSFETs, the

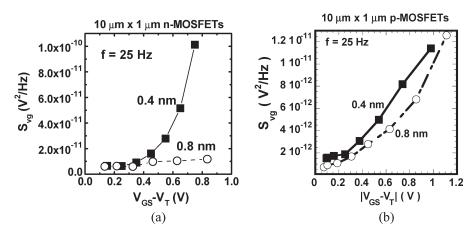

Fig. 4. Input-referred noise versus gate voltage overdrive for two different IL thicknesses for (a) n-MOSFET and (b) p-MOSFET.

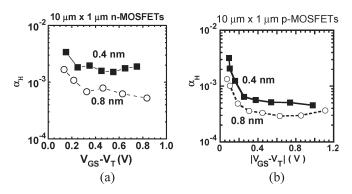

Fig. 5. Hooge's parameter versus gate voltage overdrive for two different IL thicknesses for (a) n-MOSFET and (b) p-MOSFET.

normalized  $S_{\rm id}$  shows a varying slope m that goes from 1.5 to 1, thus, it is difficult to conclude on the right fluctuation mechanism; but from normalized noise values with  $I_{\rm D}$  (not shown), the noise mechanism points to the mobility model [10], [12]. Note that for all devices, the slope m is significantly lower than 2, which corresponds to number fluctuations. For both types of MOSFETs, no significant variation in noise power is noticed for different IL thicknesses.

As shown in Fig. 4, the input-referred voltage spectral density  $S_{\rm vg} = S_{\rm id}/G_{\rm M}^2$  at f=25 Hz exhibits a pronounced dependence on the gate voltage overdrive for all devices, but not for n-MOSFETs with higher IL thickness. Higher  $S_{\rm vg}$  values are noticed for n- and p-channel transistors with 0.4 nm IL compared to 0.8 nm. For p-MOSFETs, clearly, a pronounced  $S_{\rm vg}$  dependence on gate voltage overdrive is observed, further confirming that mobility fluctuations, which cause  $S_{\rm vg} \propto |V_{\rm GS}-V_{\rm T}|$ , dominate over number fluctuations, which cause  $S_{\rm vg}$  to be independent on  $|V_{\rm GS}-V_{\rm T}|$  [9].

For a fair comparison between n- and p-MOSFETs, the Hooge's parameter [12] is considered as a figure of merit for both cases. The resulting values are plotted in Fig. 5 as a function of gate voltage overdrive. Here, the Hooge's parameter is evaluated using the following formula:

$$\alpha_{\rm H} = \frac{fWLC_{\rm ox}|V_{\rm GS} - V_T|S_{\rm id}}{qI_{\rm D}^2} \tag{1}$$

where f is the frequency,  $C_{ox}$  is the gate dielectric capacitance per unit area, and q is the elementary electron charge. A strong dependence is observed with regard to IL thickness in n- and p-MOSFETs, where the values are higher for the 0.4-nm IL thickness. The higher Hooge's parameter in lower IL thickness devices can be attributed to two different causes: higher  $C_{

m ox}$  values or lower channel mobility. The first cause can be disregarded since the observed  $\alpha_{\rm H}$  increase is significantly higher compared to the corresponding  $C_{ox}$  increase. Thus, we conclude that channel mobility is the cause. The enhanced mobility fluctuations are mainly due to lower mobility values in high- $\kappa$  gate stacks with lower IL thickness, as reported by other researchers [4], [5]. Increased mobility fluctuations for lower IL thickness can be ascribed to increased Coulomb scattering from charges in the high- $\kappa$  layer closer to the Si-SiO<sub>2</sub> interface. This conclusion is also supported by the correlation between charge density in the HfO2 layer and Coulomb scattering observed on a similar set of samples [13].

### IV. CONCLUSION

In summary, the impact of the interfacial layer thickness on the 1/f noise performance of metal-gated n- and p-channel MOSFETs with high- $\kappa$  gate dielectrics and EOTs in the range of 1 nm has been investigated. It has been shown that reducing the interfacial layer thickness from 0.8 to 0.4 nm, the mobility fluctuations mechanism becomes the main source of 1/f noise not only on pMOS devices, as usually observed, but also on nMOS devices. A higher Hooge's parameter is noticed in devices with lower IL thickness in n- and p-MOSFETs. This is mainly due to the observed scaling of the IL in these gate stacks, where bringing the high- $\kappa$  layer closer to the Si-SiO2 interface enhances the 1/f noise mainly due to mobility fluctuations.

#### REFERENCES

- [1] M. Houssa Ed., High-κ Gate Dielectrics. London, U.K.: IOP, 2003.

- [2] H. R. Huff and D. C. Gilmer Eds., High Dielectric Constant Materials-VLSI MOSFET Applications. New York: Springer-Verlag 2005.

- [3] G. Groeseneken, L. Pantisano, L.-Å. Ragnarsson, R. Degraeve, M. Houssa, T. Kauerauf, P. Roussel, S. De Gendt, and M. Heyns, "Achievements and challenges for the electrical performance of MOSFET's with high-κ gate dielectrics," in *Proc. IPFA*, 2004, pp. 147–155.

- [4] L.-Å. Ragnarsson, W. Tsai, A. Kerber, P. J. Chen, E. Cartier, L. Pantisano, S. De Gendt, and M. Heyns, "Mobility in high-κ dielectric based field effect transistors," in *Proc. SSDM*, 2003, pp. 46–47.

- [5] L.-Å. Ragnarsson, L. Pantisano, V. Kaushik, S.-I. Saito, Y. Shimamoto, S. De Gendt, and M. Heyns, "The impact of sub monolayers of HfO<sub>2</sub> on the device performance of high-κ based transistors," in *IEDM Tech. Dig.*, 2003, pp. 87–90.

- [6] G. Giusi, F. Crupi, C. Pace, C. Ciofi, and G. Groeseneken, "A comparative study of drain and gate low frequency noise in nMOSFETs with hafnium based gate dielectrics," *IEEE Trans. Electron Devices*, vol. 53, no. 4, pp. 823–828, Apr. 2006.

- [7] E. Simoen, A. Mercha, L. Pantisano, C. Claeys, and E. Young, "Low-frequency noise behavior of SiO<sub>2</sub>-HfO<sub>2</sub> dual-layer gate dielectric nMOSFETs with different interfacial thickness," *IEEE Trans. Electron Devices*, vol. 51, no. 5, pp. 780–784, May 2004.

- [8] B. Min, S. P. Devireddy, Z. Çelik-Butler, F. Wang, A. Zlotnicka, H. H. Tseng, and P. J. Tobin, "Low-frequency noise in submicrometer

- MOSFETs with  $HfO_2$ ,  $HfO_2/Al_2O_3$  and  $HfAlO_x$  gate stacks," *IEEE Trans. Electron Devices*, vol. 51, no. 10, pp. 1679–1687, Oct. 2004.

- [9] R. Jayaraman and C. G. Sodini, "A 1/f noise technique to extract the oxide trap density near the conduction band edge of silicon," *IEEE Trans. Electron Devices*, vol. 36, no. 9, pp. 1773–1782, Sep. 1989.

- [10] K. K. Hung, P. K. Ko, C. Hu, and Y. C. Cheng, "A unified model for the flicker noise in metal–oxide–semiconductor field-effect transistors," *IEEE Trans. Electron Devices*, vol. 37, no. 3, pp. 654–665, Mar. 1990.

- [11] G. Ghibaudo, O. Roux, C. Nguyen-Duc, F. Balestra, and J. Brini, "Improved analysis of low-frequency noise in field-effect MOS transistors," *Phys. Status Solidi A*, vol. 124, pp. 571–581, 1991.

- [12] F. N. Hooge, "1/f noise sources," *IEEE Trans. Electron Devices*, vol. 41, no. 11, pp. 1926–1935, Nov. 1994.

- [13] E. Simoen, A. Mercha, C. Claeys, and E. Young, "Correlation between the 1/f noise parameters and the effective low-field mobility in HfO<sub>2</sub> gate dielectric n-channel metal-oxide-semiconductor field-effect transistors," *Appl. Phys. Lett.*, vol. 85, no. 6, pp. 1057–1059, Aug. 2004.