## CADENCE LAYOUT TUTORIAL

## **Creating Layout of an inverter from a Schematic:**

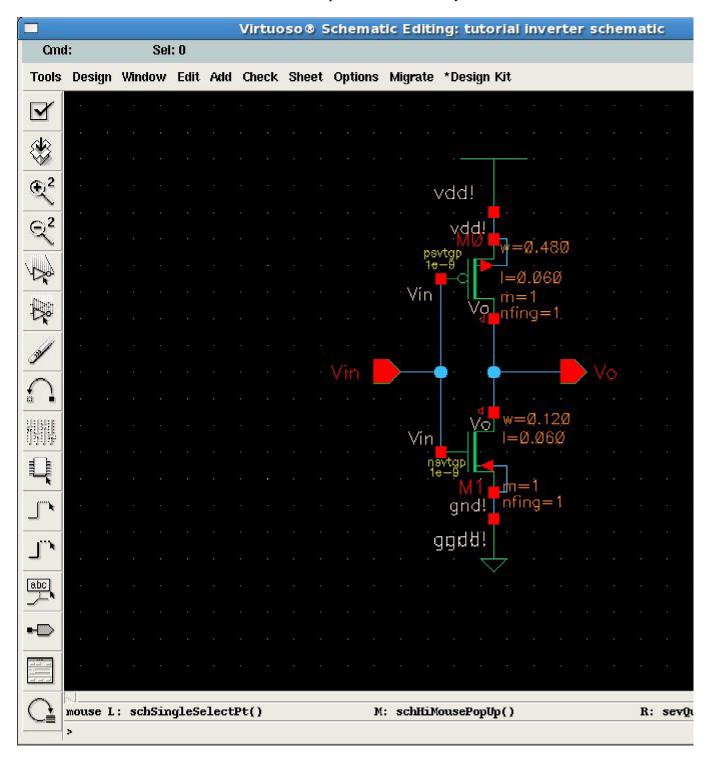

Open the existing Schematic

From the schematic editor window Tools—>Design Synthesis—>Layout XL

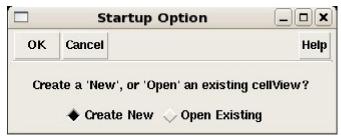

A window for startup Options comes up

Select the button corresponding to the Create New text as shown

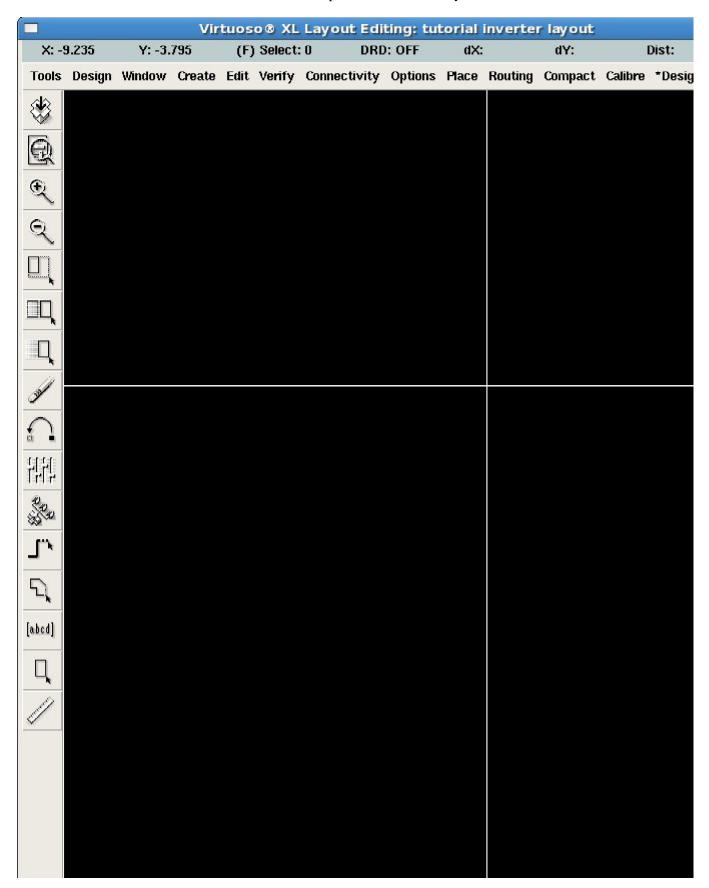

A Create New File window comes up. The Cell Name corresponds to the schematic name, leave it that way.

The field corresponding to the View Name label should read Layout.

Click OK and see the layout window come up.

From the layout window menu select:

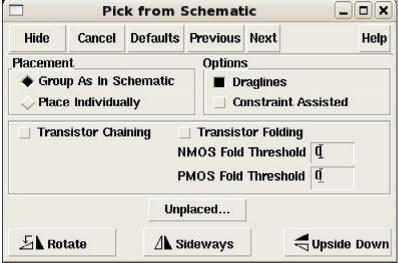

Create—>pick from Schematic and the window below comes up

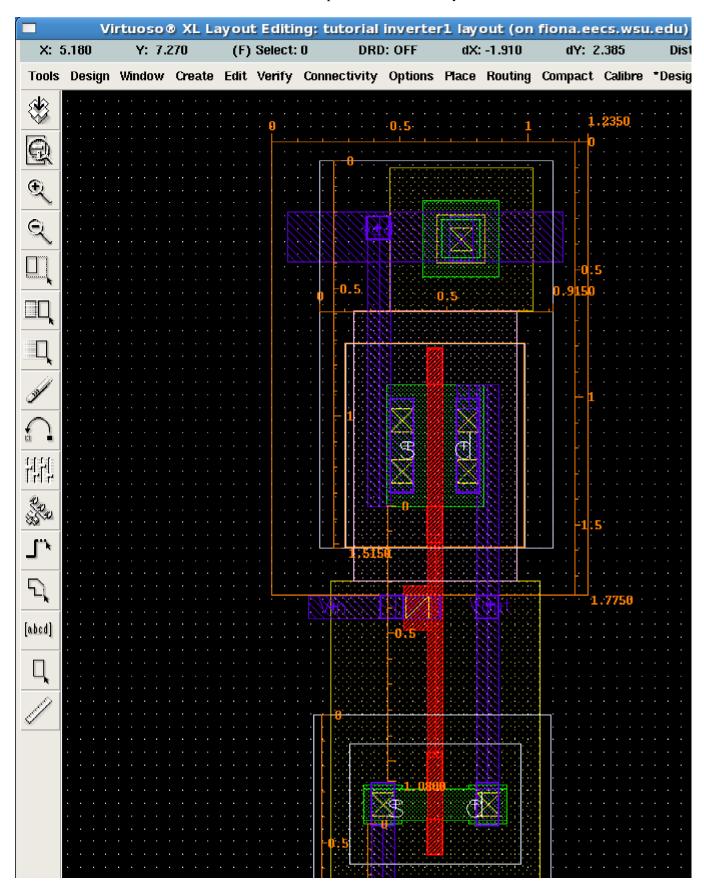

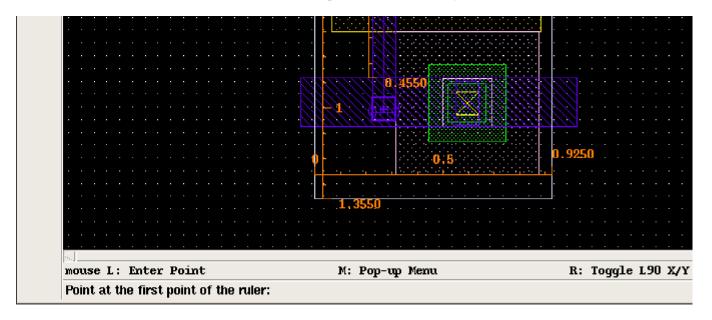

Highlight/Select the entire circuit from the schematic window and move the mouse onto the layout window. The layout components of your circuit show on the layout window. Place them with a click of the mouse. If the layers do not show; simultaneously press the SHIFT key and the letter F and the layers will show. Now connect the Poly layers using the drawing tool. This is achieved by selecting from the LSW window the P0 drawing layer and drawing a rectangle that joins the nMOS and pMOS gates (red layer on each transistor).

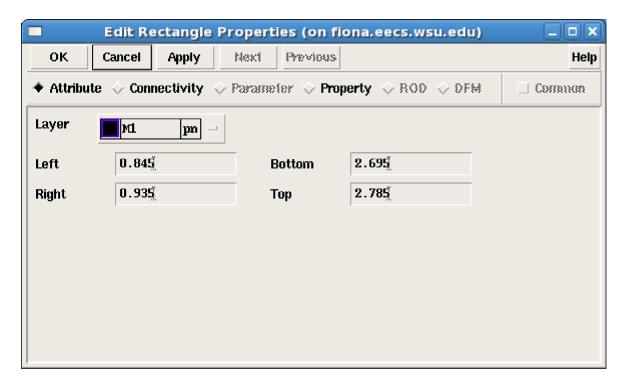

Connect the drains using the M1 drawing layer selected from the LSW window. Draw the ground and vdd nets. They will be of 0.36microns wide. See the picture below for dimensions. Use the *hot key* "i" to insert the NTAP\_J instance on the vdd net, making sure the contact is directly on the net. Insert the PTAP\_J instance on the gnd net.

## **VERY IMPORTANT**

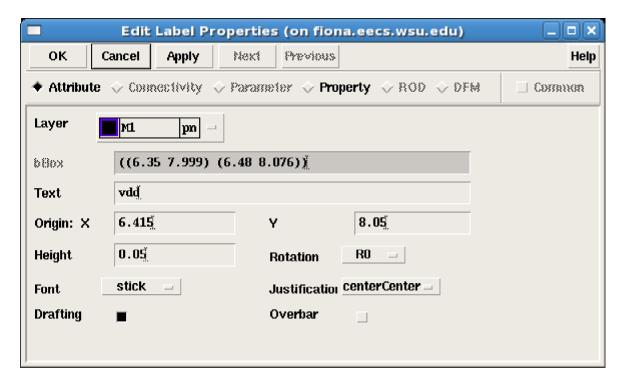

Labels must use the pin layers instead of the text. See diagram below. To view the properties and connectivity of the pin: select the pin and click the middle mouse button to select properties. The same should be done with the text box.

Make sure the pin and the text are of the corresponding layer e.g if the pin is a P0 pin make sure it is placed on P0 layer and the text must be of P0 material.

$file: /\!/ Zeus/class \$/ ee 466/public\_html/tutorial/layout.html$

Page 8

file://Zeus/class\$/ee466/public\_html/tutorial/layout.html

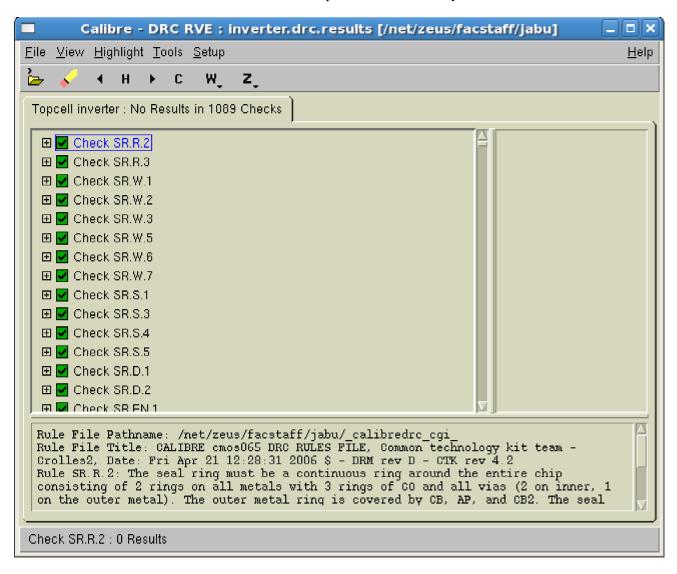

The layout is now complete and needs to be checked for design rule violations. On the layout window click on the Calibre menu item:

Caliber—>Run DRC

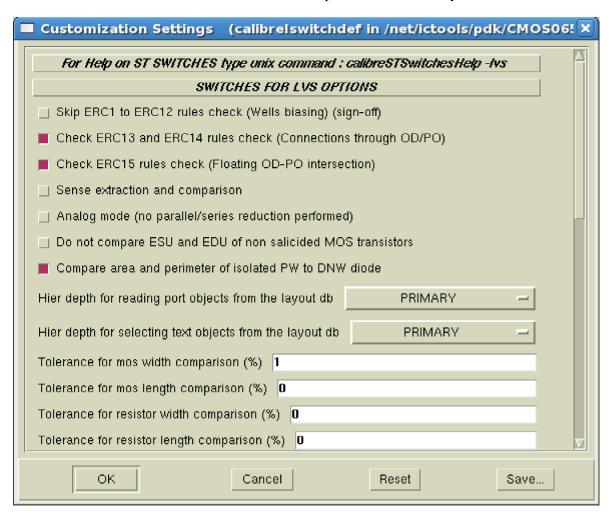

We will use the default selection. Click OK on the window above.

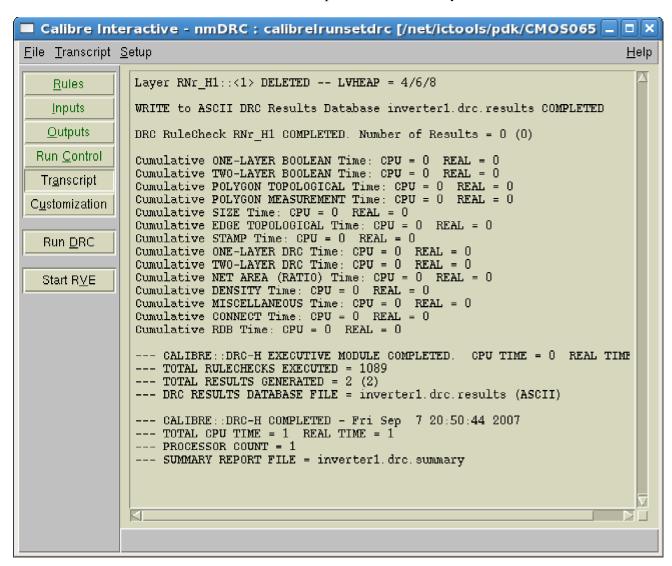

Click on Run DRC and two more windows will show up. The one that shows first does not contain information of interest. The second one is key.

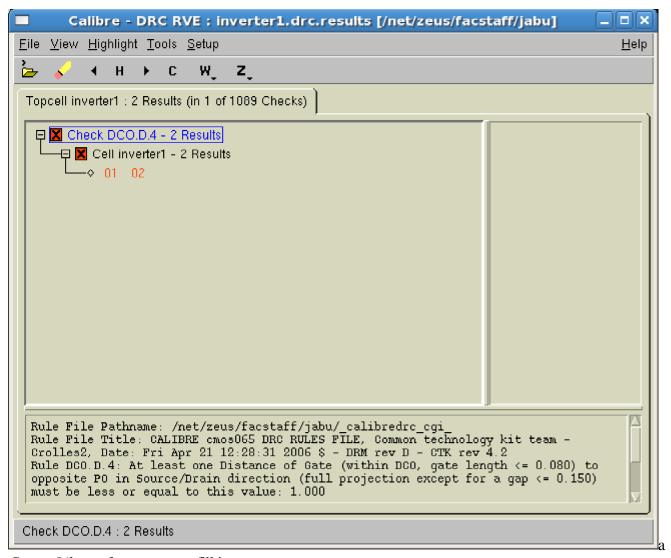

The window below shows results of a layout that has an error. Watch the comments at the bottom of the window, they give the specifics on what the error is.

Create Library form appears, fill it as

Right Click on top of the lettering highlighted in blue on the window above and watch the layout window closely. The area that has the error gets highlighted. Sometimes the color used to highlight is the same as the color of the material making it difficult to see where the error is. If you click on the numbers 01 or 02, you will see on the right hand column of this window the coordinates and you can thus click on these coordinates and watch the response on the layout window.

Correct the error and run DRC again to see if an more violations exist. The DRC Window below shows results of an error free layout, one in which no design rules have been violated.

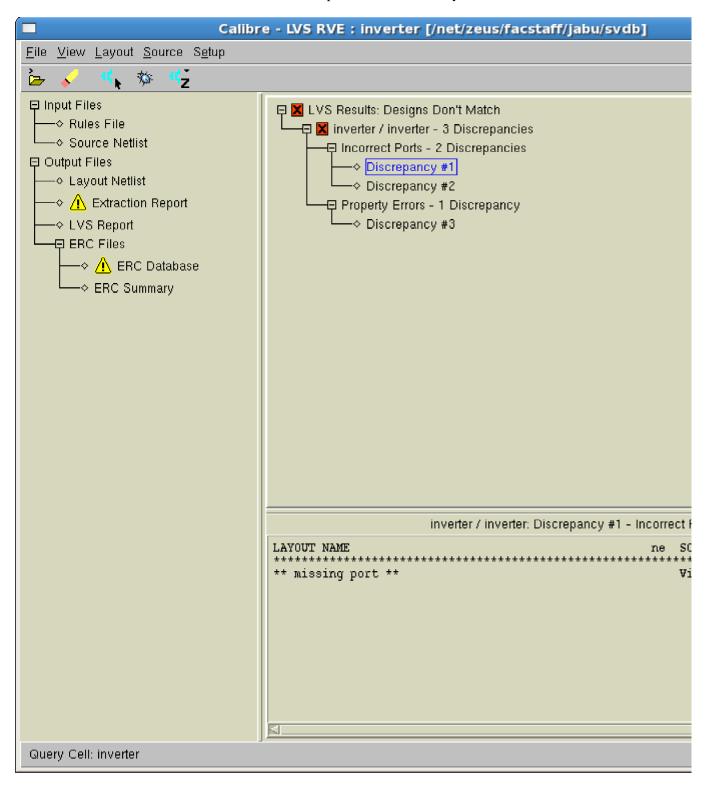

Once we have succeeded with DRC we need to compare the layout vs the schematic using LVS. Click on the Caliber menu item:

Caliber—>Run LVS

The window below shows a failed LVS. Clicking on the lettering highlighted in blue shows what the problem is.

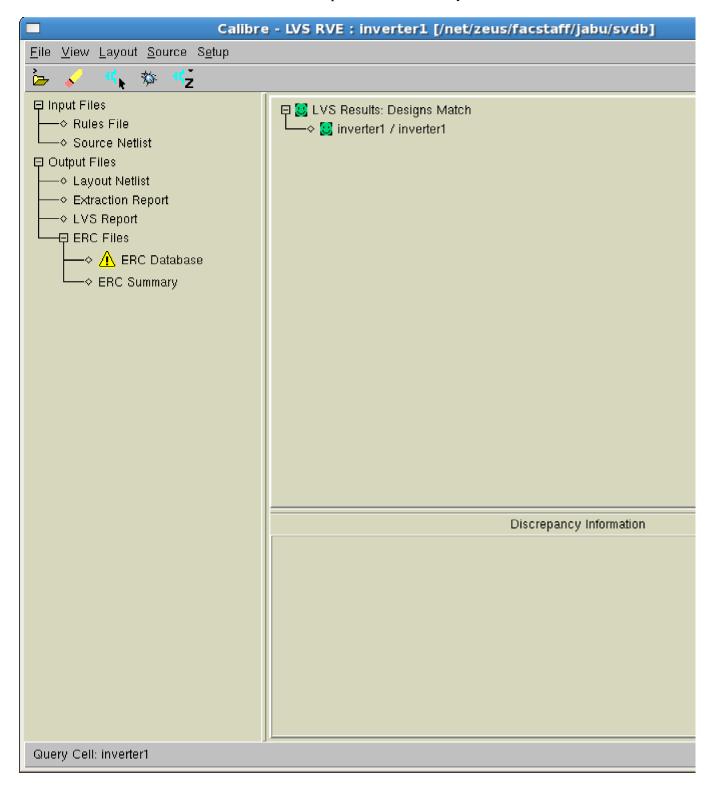

Fix the errors and re-run LVS, Note the green faces indicating success.

Now that DRC and LVS have passed close these windows and on the Layout window click on the Tools menu item:

Tools—>Post-Layout Simulation—>Schematic With Skipped Cells.

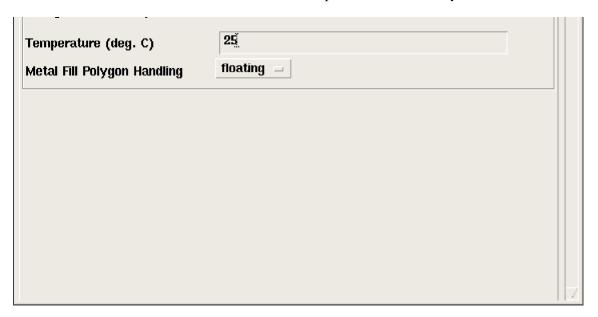

The Window below comes un.

| file://Zeus/class\$/ee466/public_html/tutorial/layout.htm |

|-----------------------------------------------------------|

| <br>r.                                                    |

| ■ Post-Layout Simulation (Schema                             | atic with Skippe | ed Cells) (on fic | one 🗕 🗆 🗙 |  |

|--------------------------------------------------------------|------------------|-------------------|-----------|--|

| Status: Ready Results: pls1 15                               |                  |                   |           |  |

| Session Tools Commands Outputs Run Log Results Help          |                  |                   |           |  |

| Top SchematicTop Layout                                      |                  |                   |           |  |

| Library tutorial                                             | Library          | tutorial          |           |  |

| Cell Browse inverter!                                        | Cell             | inverter1         |           |  |

|                                                              |                  |                   |           |  |

| View schematic                                               | View             |                   |           |  |

| Run PLS PLS 1.4.1 (C) STMicroelectronics (2007) Nets Browser |                  |                   |           |  |

| LVS<br>& Skipped Cells Extraction Reduction Back-Annotation  |                  |                   |           |  |

| Open Schematic                                               |                  |                   |           |  |

| List of Nets                                                 |                  |                   |           |  |

| Ground Net Name for Lumped Parasitic Capacitances gnd!       |                  |                   |           |  |

| Extraction Methodology RCc -                                 |                  |                   |           |  |

| Cc threshold - unit: F                                       |                  |                   |           |  |

| Cc percentage - unit: %                                      |                  |                   |           |  |

| Cg threshold for filtering - unit: F                         |                  |                   |           |  |

| Rel accuracy goal - unit: %                                  |                  |                   |           |  |

| Cap accuracy goal - unit: fF                                 |                  |                   |           |  |

| Run time limit - unit: hours                                 |                  |                   |           |  |

| Extraction Strategy RCMAX                                    |                  |                   |           |  |

| Change Default Temperature ?                                 |                  |                   |           |  |

Select the Extraction Button and then Click on Run PLS

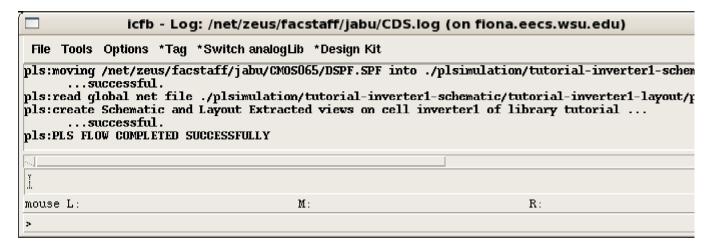

Watch the icfb window. If the extraction is completed successfully you will see the text in the figure below otherwise a message that reads: "pls:PLS Failed" will be displayed and you will have to determine the problem and fix it. If your design had not passed LVS you will get a Warning Message that states that the Schematic and the Layout are not compatible. You can proceed with the subsequent steps even though LVS failed.

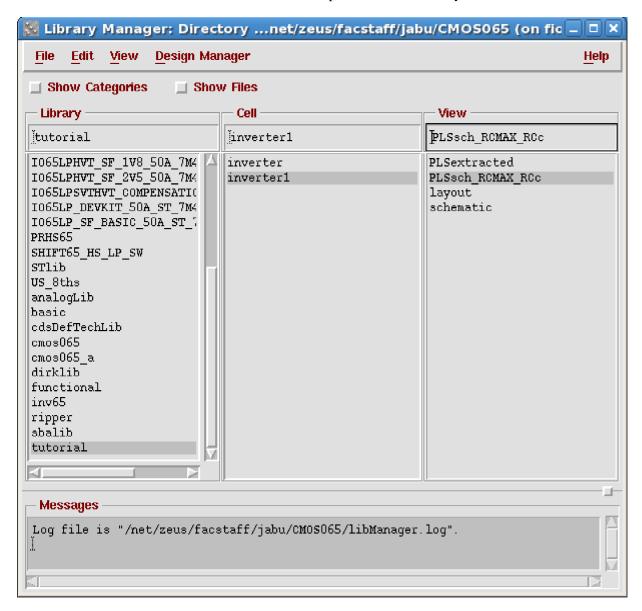

Now you have extracted schematic and layout views of your layout with all the parasitics. The library manager quits automatically at this point (should not happen but ....). Close the schematic and layout editing windows.

Open the library manager and select your library.

Notice the additional files that have been created (PLSextracted and PLSsch\_RCMAX\_RCc), open the PLSsch\_RCMAX\_RCc fil). It contains the schematic of your transistors as extracted from the layout with all the paracitics (capacitances and resistances). From this schematic window select the Tools menu item as shown in the figure below:

Tools—>Analog Environment