APPLIED PHYSICS LETTERS VOLUME 74, NUMBER 21 24 MAY 1999

## Plasma process-induced band-gap modifications of a strained SiGe heterostructure

P. K. Swain,  $^{a)}$  S. Madapur,  $^{b)}$  and D. Misra $^{c)}$

Microelectronics Research Center, Department of Electrical and Computer Engineering, New Jersey Institute of Technology, Newark, New Jersey 07102-1982

(Received 11 January 1999; accepted for publication 23 March 1999)

Exposure to plasma etching and subsequent annealing can relax the strain of coherently strained SiGe. This work investigates the change in valence-band discontinuity in plasma-exposed SiGe films due to strain relaxation by a capacitance-voltage (C-V) profiling technique using metal-oxide-semiconductor structures. Dry and wet etched samples annealed at 500, 600, 700, and 800 °C were investigated. Valence-band discontinuity  $\Delta E_V$  at the Si/SiGe interface reduced with annealing temperature and completely disappeared at higher temperature annealing. Dry etched samples demonstrated a faster relaxation mechanism as compared to their wet etched counterparts. The C-V method has turned out to be a simple, fast, and efficient approach to estimate any band-gap modifications in SiGe due to process-induced damage. © 1999 American Institute of Physics. [S0003-6951(99)01921-X]

Reliability and electrical performance of strained Si/ SiGe/Si heterostructure devices 1-4 may be significantly affected by plasma processing during device manufacturing.<sup>5</sup> Creation of strain-relieving misfit dislocation and/or threading dislocations may be possible when strained  $Si_{1-x}Ge_x$ films are processed using reactive ion etching (RIE).<sup>5</sup> Though reactive ion etching of Si has been studied in detail, 6,7 not much is known about SiGe at present. In bulk semiconductors annealing causes condensation of point defects into dislocation loops which then shrink and disappear after further annealing. However, it is well known that SiGe samples thicker than the critical thickness, as per Matthews and Blakeslee,8 annealed at temperatures higher than the growth temperature will have dislocation loops induced. The presence of such dislocation loops is known to relax the coherent strain of the SiGe layer. The strain relaxation mechanism for plasma etched samples annealed at temperatures lower than the growth temperature will be predominantly governed by the dislocation loops generated by plasma etching. On the other hand, for samples annealed above the growth temperature, the mechanism could be either due to plasma etching or due to the fact that the samples were annealed at a temperature higher than the growth temperature or both. Relaxation in strain (as a consequence of plasma etching and subsequent annealing) is expected to increase the band gap by reducing the valence-band discontinuity, and which eventually will reduce the carrier mobility in the fabricated device. Wet etching, on the other hand, is known to be a rather nondestructive method, and hence, retains the characteristics of the starting materials after the processing is

In this letter we have employed a capacitance-voltage (C-V) profiling technique to estimate the band gap of SiGe films exposed to plasma etching and subsequent annealing. Samples, with the cap layer partially removed by the plasma

etch, were studied in this work. Wet etched samples were used for comparison. C-V profiling is a fast and efficient approach to estimate plasma process-induced band-gap modifications since measurement techniques such as photoemission measurement, x-ray photoelectron spectroscopy, or photoreflectance measurement can be time consuming.

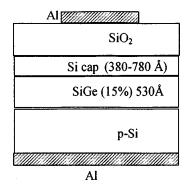

Typically, 15% of Ge is used to grow strained SiGe films for high-mobility advantages. Undoped 500-Å-thick  $Si_{1-x}Ge_x$  (x=0.15) were grown on a p-Si (2×10<sup>16</sup> cm<sup>-3</sup>) substrate by conventional chemical-vapor deposition (CVD) at 700 °C at atmospheric pressure. A 1500–1900-Å-thick Si cap layer was deposited on the Si<sub>1-x</sub>Ge<sub>x</sub> layer. It should be noted here that the thickness of our SiGe sample (with 15% Ge) is more than the critical thickness as per Matthews and Blakeslee, which is 190 Å.8 Plasma etching was performed in a DRYTECH 100 plasma reactor at a chamber pressure of 150 mTorr with a flow rate of 50 sccm SF<sub>6</sub> and freon 115 each. The rf power was 400 W. The etch rate was 40 Å/s and etching was continued for 28 s for partial removal of the cap layer (approximately 1100). On the other hand, wet etching was carried out in a solution of 25 mg KOH, 1 mg K<sub>2</sub>Cr<sub>2</sub>O<sub>7</sub>, 25 ml propanol in 100 ml of water at 26 °C. The etch rate was 160 Å/min and etching was continued for 7 min. Both the dry and wet etched samples were annealed at temperatures of 500, 600, 700, and 800 °C for 60 s in a rapid thermal process (RTP) reactor under vacuum. SiO<sub>2</sub> was then deposited by low-pressure CVD at 450 °C. The thickness of SiO<sub>2</sub> was 400 Å. Al dots were then evaporated through a metal mask by thermal evaporation to make metal-oxidesemiconductor (MOS) capacitors. Back contact was made with Al deposition on the Si substrate. A postmetal annealing was carried out at 350 °C in N2 ambient. A completed sample is shown in Fig. 1. High-frequency C-V measurements were performed using 4145B semiconductor parameter analyzer and a Boonton 71BD capacitance meter.

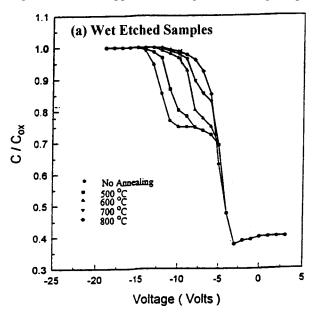

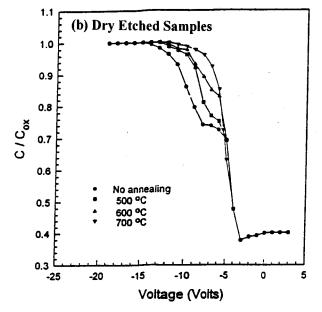

Figure 2(a) shows a typical C-V profile obtained for the wet etched samples. The presence of a distinct kink in the unannealed sample in Fig. 2(a) indicates that the SiGe layer is coherently strained. However, the nature of the kink changed as the annealing was performed at temperatures of

a) Currently at Sarnoff Corporation, 201 Washington Road, CN5300, Princeton, NJ 08543-5300.

b)Currently at Anadigics Inc., 35 Technology Drive, Warren, NJ 07059.

c)Corresponding author. Electronic mail: dmisra@megahertz.njit.edu

FIG. 1. Schematic drawing of the MOS device structure used for investiga-

500, 600, and 700 °C. No such kink was observed for samples annealed at 800 °C. On the other hand, as shown from the C-V plots obtained for the dry etched sample [Fig. 2(b)], a kink is observed for the unannealed sample. As the sample is annealed at 500 and 600 °C, the shape of the kink changes before it disappears with higher annealing tempera-

FIG. 2. C-V plot obtained for the wet etched samples (a) and dry etched samples (b) annealed at different temperatures.

FIG. 3. Hole confinement in the quantum well leading to the kink in the C-V measurements

tures. A comparison of Figs. 2(a) and 2(b) indicates that the kinks obtained for the dry etched 500 and 600 °C samples are similar to the ones obtained for the wet etched sample annealed at 600 and 700 °C, respectively.

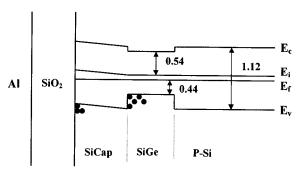

To explain the appearance of such kinks a simple model is proposed. When the MOS device is driven into accumulation from inversion, the substrate being p-type Si, holes are attracted from the bulk towards the interface, under the action of increased negative voltage. In the absence of the strained SiGe layer the holes are expected to accumulate uninterruptedly at the oxide/Si cap interface. Under such a condition, a continuous increase in capacitance is expected until it reaches a constant maximum value equal to  $C_{ox}$ . However, in the presence of a strained SiGe layer, as in our case, some holes on their way towards the oxide/Si interface are trapped within the quantum well (QW) as a consequence of band-gap narrowing due to coherent strain. As shown in Fig. 3, hole confinement results in a decrease in the total capacitance because of the series combination of  $C_{\text{ox}}$  and  $C_{\text{SiGe OW}}$ . The capacitance of the cap layer is neglected as the device was driven into accumulation. When the applied voltage becomes more negative, such that the holes confined inside the quantum well are negligibly small compared to holes accumulated at the oxide/Si interface, the capacitance increases and finally equals  $C_{ox}$ . This mechanism results in the appearance of a distinct kink for the wet etched unannealed sample. However, as the sample is annealed at 500, 600, and 700 °C, the coherent strain in the SiGe layer is reduced, and hence, the band-gap narrowing effect also decreases. This spreading of the band gap results in a decrease in the well height (amount of discontinuity in the valence-band edge:  $\Delta E_V$ ). Hence, the number of holes captured in the well decreases, thus allowing a larger number of holes to accumulate at the oxide/Si interface for the same applied potential. This mechanism results in an increase of capacitance for the samples annealed at a higher temperature as compared to their low-temperature counterparts. Samples annealed at 800 °C show no such kink, indicating the absence of the hole capture mechanism. This clearly indicates that the coherent strain in SiGe is lost, resulting in complete relaxation of the SiGe layer. The appearance of kinks for the dry etched samples can also be explained by a similar mechanism. However, the kink for the unannealed dry etched sample shows a reduced number of holes in the quantum well, indicating partial relaxation.

A numerical estimate of the band gap for the plasma as well as wet etched samples annealed at different temperatures can be made by making use of the hole density of state

TABLE I. Value of  $(1 - [C/C_{ox}])$  and the calculated band gap in eV for the dry as well as wet etched samples after being annealed at different temperatures.

|                                |            | No<br>annealing   | 500 °C         | 600 °C          | 700 °C      | 800 °C |

|--------------------------------|------------|-------------------|----------------|-----------------|-------------|--------|

| $(1-[C/C_{\rm ox}])$           | Wet<br>Dry | 0.2375<br>0.13125 | 0.1875<br>0.05 | 0.0625<br>0.016 | 0.0187<br>0 | 0      |

| Calculated<br>band gap<br>(eV) | Wet        | 1.013             | 1.019          | 1.048           | 1.079       | 1.10   |

|                                | Dry        | 1.034             | 1.054          | 1.083           | 1.10        | 1.10   |

in the valance band. The number of holes captured in the quantum well is directly related to the valance-band discontinuity occurring due to coherent strain in the SiGe film. It is well known that the number of holes near the valance band is given by<sup>9</sup>

$$p = N_v \exp[-(E_f - E_v)/kT]/\text{cm}^3,$$

(1)

where

$$N_V = 2[2m_{dh}kT/h^2]^{3/2}/\text{cm}^3,$$

(2)

where,  $m_{\rm dh}=$  hole effective mass. Wang *et al.* <sup>10</sup> have reported a value of 0.44 mo for the hole effective mass for their sample (Si/Si<sub>0.85</sub>Ge<sub>0.15</sub>/Si), which is identical to ours. In this case, the valance-band maximum of Si<sub>0.85</sub>Ge<sub>0.15</sub> is ~75 meV lower than that of Si, assuming  $\Delta E_v \gg \Delta E_c$ . <sup>10</sup> Substituting the value of  $m_{dh}$  in Eq. (2) we get  $N_v = 3.654 \times 10^{24} \, {\rm cm}^{-3}$ . The number of holes captured inside the quantum well can be calculated from the C-V curve (Fig. 2) by the following method. Values of  $\{1-(C/C_{\rm ox})\}$  at a given applied bias for samples (dry as well as wet etched and subsequently annealed) are summarized in Table I.

The value of  $C_{\rm ox}$ , calculated using the simple formula  $(k\epsilon_0A/d)$ , where A= area of the MOS device (diameter: 300  $\mu$ m), k= dielectric constant for the oxide (3.9), and d= thickness of the SiO<sub>2</sub> layer (400 Å) is 61 pF. Using the value of  $C_{\rm ox}$ ,  $C_{\rm SiGe\ QW}$  can be calculated for all the samples. Multiplying C with the applied bias, V (10 V), the total charge (Q) can be estimated. Dividing Q by the electronic charge would give the number of holes trapped in the quantum well, which will allow us to compute the hole density  $p/{\rm cm}^3$ . The value of "p," thus calculated, for the wet etched, unannealed sample is  $0.2036\times 10^{18}/{\rm cm}^3$  (for  $C_{\rm SiGe\ QW}=195\times 10^{-12}\ {\rm F}$ ). Substituting "p" in Eq. (1), we obtain

$$3.654 \times 10^{24} \exp[-(E_f - E_v)/kT] = 0.2036 \times 10^{18}/\text{cm}^3$$

. (3)

Simplifying Eq. (3) gives

$$(E_f - E_p) = 0.434 \text{ eV}.$$

(4)

Using similar methodology, the  $(E_f - E_v)$  values were computed for all the samples. It is known that the band discontinuity for strained SiGe occurring at the conduction band is much smaller as compared to the valance band and has a value of 0.02 eV. So,  $(E_c - E_i)$  has a value of  $[(1.12/2) - 0.02] = 0.54 \, \mathrm{eV}$ , for the strained SiGe film, where 1.12 eV is the band gap of Si. The band gap  $(E_c - E_v)$  can be expressed by the following:

$$(E_c - E_v) = (E_c - E_i) + (E_i - E_f) + (E_f - E_v)$$

eV. (5)

Substituting the value of  $(E_f - E_v)$ , in Eq. (5), the band gap for the samples can be calculated and is summarized in Table T

Since wet etching is known to be a nondestructive technique, the wet etched unannealed samples would be coherently strained. Hence, the band gap of such samples would be less than the silicon band gap by a factor of  $(\Delta E_n)$  $+\Delta E_c$ ). As seen from Table I, the band gap for the wet etched unannealed sample is 1.013 eV. Also,  $\Delta E_v$  and  $\Delta E_c$ have values of 0.075 and 0.020 eV, 10 which are in agreement with the silicon band gap. It may also be seen from Table I that the band gap increases progressively to 1.10 eV with increase in annealing temperature to 800 °C. This indicates that the coherent strain in the SiGe layer is becoming relaxed with the increase in annealing temperature and a complete relaxation takes place at 800 °C. The relaxation of the samples annealed at 500, 600, and 700 °C can be considered to be predominantly due to the creation of dislocation loops due to RIE and their subsequent annealing. As the SiGe samples were grown at 700 °C, these samples when annealed at 800 °C will have dislocation loops induced causing relaxation. Also, plasma etching of these samples will enhance the relaxation mechanism. On the other hand, a comparison of band-gap values for the dry and wet etched samples annealed at a given temperature indicate a higher value for the dry etched samples. This indicates an advanced relaxation mechanism in the dry etched samples. Also, as may be seen from Table I, the dry etched, 700 °C annealed sample has a band gap of 1.10 eV, indicating a complete strain relaxation takes place at a lower temperature as opposed to 800 °C for the wet etched samples.

In conclusion, the effect of plasma etching and subsequent annealing on the valence-band discontinuity  $E_V$  at the Si/SiGe interface was studied. Dry etched samples demonstrated a faster relaxation mechanism as compared to their wet etched counterparts. In both dry and wet etched samples as the annealing temperature increases the valence-band discontinuity is reduced and completely disappeared at higher temperature annealing. A simple technique is proposed to measure the band gap of the SiGe films by a C-V measurement using a MOS structure.

This work is supported by National Science Foundation Grant No. ECS-9207665.

<sup>&</sup>lt;sup>1</sup>P. W. Li, E. S. Yang, Y. F. Yang, J. O. Chu, and B. S. Meyerson, IEEE Electron Device Lett. **15**, 402 (1994).

<sup>&</sup>lt;sup>2</sup>S. Verdonckt-Vardebroek, E. F. Crabbe, B. S. Meyerson, D. L. Harame, P. J. Restle, J. M. C. Stork, and J. B. Johnson, IEEE Trans. Electron Devices 41, 90 (1994).

<sup>&</sup>lt;sup>3</sup>P. M. Garone, V. Venkataraman, and J. C. Sturm, IEEE Electron Device Lett. **13**, 56 (1992).

<sup>&</sup>lt;sup>4</sup>K. Goto, J. Murota, T. Maeda, R. Schutz, K. Aizawa, R. Kircher, K. Yokoo, and S. Ono, Jpn. J. Appl. Phys., Part 1 32, 438 (1993).

R. Braunstein, A. R. Moore, and F. Herman, Phys. Rev. 109, 695 (1958).

J. W. Coburn, *Plasma Etching and Reactive Ion Etching* (American Vacuum Society, New York, 1982).

<sup>&</sup>lt;sup>7</sup>For a review see, e.g., G. S. Oehrlein, in *Handbook of Plasma Processing Technology*, edited by S. M. Rossnagel, J. J. Cuomo, and W. D. Westwook (Noyes, Park Ridge, NJ, 1990), p. 196.

<sup>&</sup>lt;sup>8</sup>J. M. Matthews and A. E. Blakeslee, J. Cryst. Growth 27, 118 (1974).

<sup>&</sup>lt;sup>9</sup>S. M. Sze, *Physics of Semiconductor Devices* (Wiley-Interscience, New York, 1969), p. 27.

<sup>&</sup>lt;sup>10</sup> P. J. Wang, F. F. Fang, B. S. Meyerson, J. Nocera, and B. Parker, Appl. Phys. Lett. **54**, 2701 (1989).