### Virtuoso Analog Design Environment: iModule 1 for iLS

Version 5.1.41

**iLS LHS/TOC**

February 10, 2005

© 1990-2005 Cadence Design Systems, Inc. All rights reserved. Printed in the United States of America. Cadence Design Systems, Inc., 555 River Oaks Parkway, San Jose, CA 95134, USA

#### **Cadence Trademarks**

- 1st Silicon Success® Allegro® Assura<sup>TM</sup> **BuildGates®** Cadence<sup>®</sup> (brand and logo) CeltIC<sup>TM</sup> ClockStorm® CoBALT<sup>TM</sup> Conformal® Connections® Design Foundry® Diva® Dracula® Encounter<sup>TM</sup> Fire & Ice® First Encounter®

- FormalCheck® HDL-ICE® Incisive<sup>TM</sup> IP Gallery<sup>™</sup> Nano Encounter<sup>TM</sup> NanoRoute<sup>TM</sup> NC-Verilog® OpenBook® online documentation library Orcad® Orcad Capture® Orcad Layout® PacifIC<sup>™</sup> Palladium<sup>TM</sup> Pearl® PowerSuite<sup>™</sup> **PSpice**®

- QPlace<sup>®</sup> Quest<sup>®</sup> SeismIC<sup>TM</sup> SignalStorm<sup>®</sup> Silicon Design Chain<sup>TM</sup> Silicon Ensemble<sup>®</sup> SoC Encounter<sup>TM</sup> SourceLink<sup>®</sup> online customer support Spectre<sup>®</sup> TtME<sup>®</sup> UltraSim<sup>®</sup> Verifault-XL<sup>®</sup> Verilog<sup>®</sup> Virtuoso<sup>®</sup> VoltageStorm<sup>®</sup>

#### **Other Trademarks**

All other trademarks are the exclusive property of their respective owners.

#### **Confidentiality Notice**

No part of this publication may be reproduced in whole or in part by any means (including photocopying or storage in an information storage/retrieval system) or transmitted in any form or by any means without prior written permission from Cadence Design Systems, Inc. (Cadence).

Information in this document is subject to change without notice and does not represent a commitment on the part of Cadence. The information contained herein is the proprietary and confidential information of Cadence or its licensors, and is supplied subject to, and may be used only by Cadence's customer in accordance with, a written agreement between Cadence and its customer. Except as may be explicitly set forth in such agreement, Cadence does not make, and expressly disclaims, any representations or warranties as to the completeness, accuracy or usefulness of the information contained in this document. Cadence does not warrant that use of such information will not infringe any third party rights, nor does Cadence assume any liability for damages or costs of any kind that may result from use of such information.

RESTRICTED RIGHTS LEGEND Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

UNPUBLISHED This document contains unpublished confidential information and is not to be disclosed or used except as authorized by written contract with Cadence. Rights reserved under the copyright laws of the United States.

# Table of ContentsVirtuoso Analog Design Environment iModule 1

#### Virtuoso Analog Design Environment iModule 1: Schematic Entry and Simulation

| Module 1 | Introduction to the Analog Design Environment, Version 5.1.41 |  |

|----------|---------------------------------------------------------------|--|

|          | Topics in this Module                                         |  |

|          | Course Objectives                                             |  |

|          | Getting Help                                                  |  |

|          | What's New in 5.1.41                                          |  |

|          | Overview of Virtuoso Analog Design Environment                |  |

|          | Design System Initialization Files                            |  |

|          | Overview of the Design Framework II Environment               |  |

|          | Advantages of Using Design Framework II                       |  |

|          | The Command Interpreter Window (CIW)                          |  |

|          | Using a Form                                                  |  |

|          | Initializing the Design Framework II Environment              |  |

|          | IC Design Flow, Front to Back                                 |  |

|          | The Library Manager                                           |  |

|          | The Library Structure                                         |  |

|          | Creating a New Library                                        |  |

|          | Shared Technology Library                                     |  |

|          | Technology File Stored in the Design Library                  |  |

|          | Overview of Circuit Simulation                                |  |

|          | Types of Circuit Simulation Analyses                          |  |

|          | Summary                                                       |  |

|          | Labs for Module 1                                             |  |

|          | Lab 1-1 Setting Up the Database                               |  |

|          | Lab 1-2 Getting Started                                       |  |

|          | Starting the Online Help, CDSDoc                              |  |

|          | Starting the Cadence Software                                 |  |

|          | Lab 1-3 Top-Down System Modeling                     | 1-5  |

|----------|------------------------------------------------------|------|

|          | Design Flow                                          | 1-5  |

|          | Opening the Peak Detector Circuit                    | 1-5  |

|          | Viewing the AHDL Description                         | 1-7  |

|          | Running Simulation                                   | 1-8  |

|          | Choosing a Simulator                                 | 1-8  |

|          | Setting the Model Libraries                          | 1-9  |

|          | Choosing Analyses                                    | 1-9  |

|          | Saving Outputs for Plotting                          | 1-10 |

|          | Running the Simulation                               | 1-12 |

| Module 2 | Schematic Entry                                      |      |

|          | Topics in this Module                                |      |

|          | Schematic Entry Flow                                 |      |

|          | Contents of a Schematic                              |      |

|          | Creating a New Cellview                              |      |

|          | Adding Component Instances                           | 2-11 |

|          | Updating Design Objects                              | 2-13 |

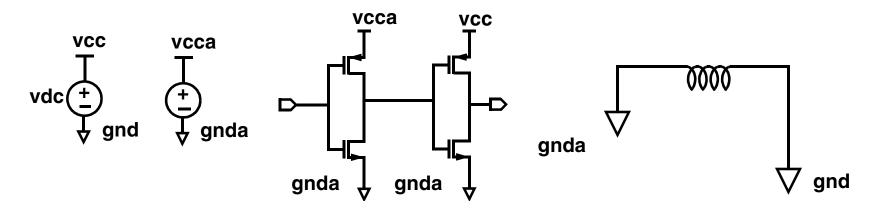

|          | Adding Sources and Ground                            | 2-15 |

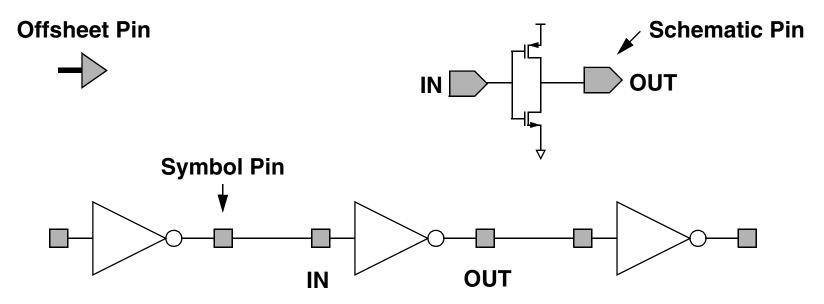

|          | Pins                                                 | 2-17 |

|          | Wires and Wire Labels                                | 2-19 |

|          | Interconnecting Components                           | 2-21 |

|          | Schematic Checking                                   | 2-23 |

|          | Schematic Checking Rules                             | 2-25 |

|          | Component Parameter Types                            | 2-27 |

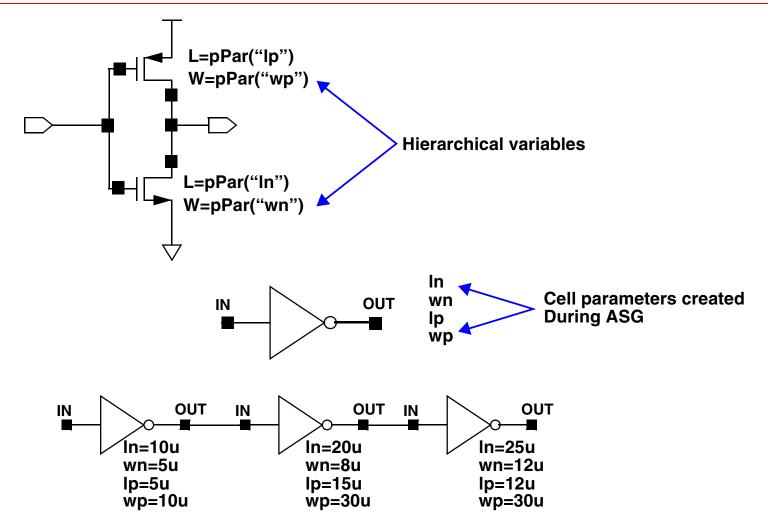

|          | Passing Parameters Through the Hierarchy             | 2-29 |

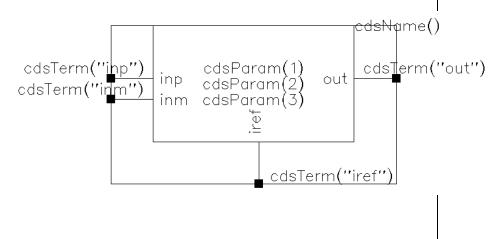

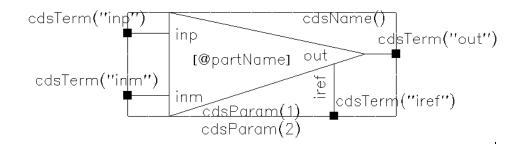

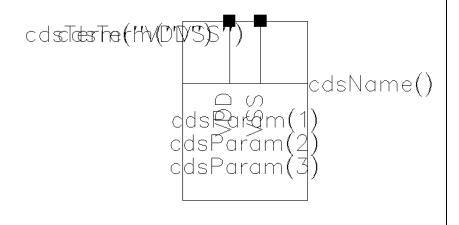

|          | Symbol Generation                                    | 2-31 |

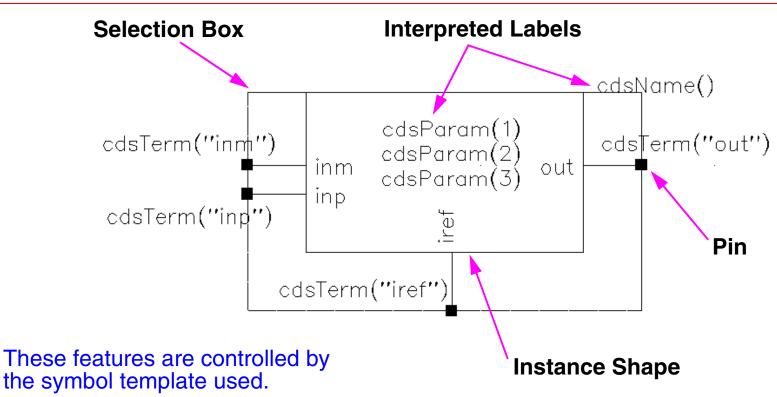

|          | Characteristics of an Automatically Generated Symbol | 2-33 |

|          | Schematic Window Icons and Accelerator Keys          | 2-35 |

|          | Schematic Editor Command Summary                     |      |

|          | Bindkeys (Accelerator Keys)                          | 2-39 |

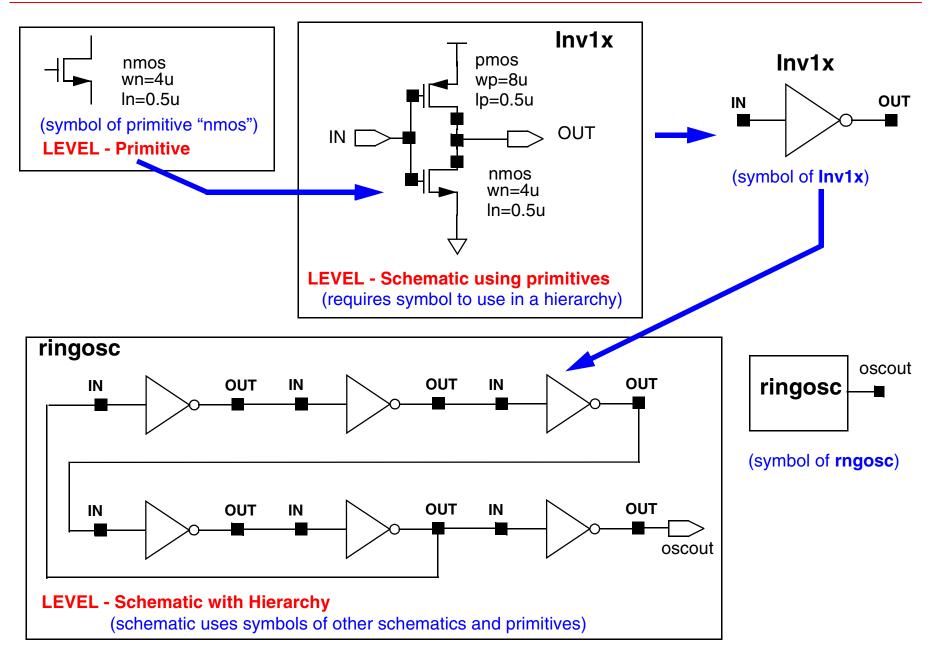

|          | Using a Hierarchy                                    | 2-41 |

|          | Lab Reference Material: Mouse Buttons                | 2-43 |

| Labs for Module 2                           |  |

|---------------------------------------------|--|

| Lab 2-1 Schematic Entry                     |  |

| Creating a Library                          |  |

| Creating a Schematic Cellview               |  |

| Adding Components to a Schematic            |  |

| Adding Pins to a Schematic                  |  |

| Adding Wires to a Schematic                 |  |

| Adding Net Names                            |  |

| Saving a Design                             |  |

| Lab 2-2 Symbol Creation                     |  |

| Creating a Symbol                           |  |

| Editing a Symbol                            |  |

| Adding Text to a Symbol                     |  |

| Saving a Symbol                             |  |

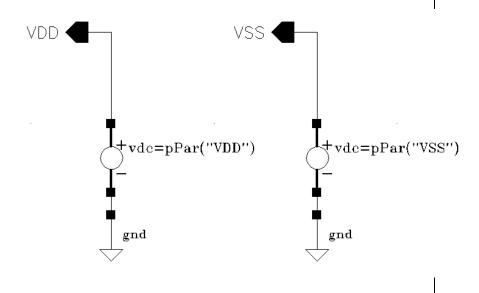

| Lab 2-3 Building the Supply Circuit         |  |

| Creating the <i>supply</i> Cellview         |  |

| Building the <i>supply</i> Circuit          |  |

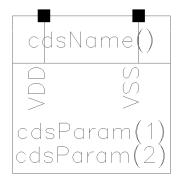

| Creating a Symbol                           |  |

| Notes on Symbol Updates                     |  |

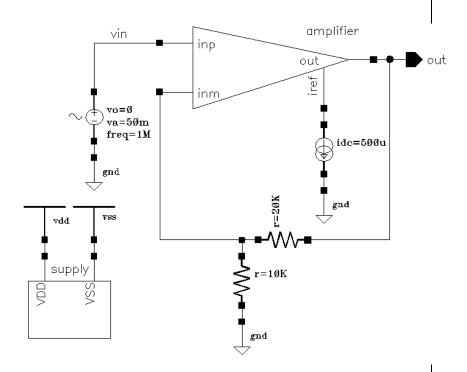

| Lab 2-4 Building the ampTest Design         |  |

| Creating the <i>ampTest</i> Cellview        |  |

| Building the <i>ampTest</i> Circuit         |  |

| Module 3 Analog Simulation                  |  |

| Topics in this Module                       |  |

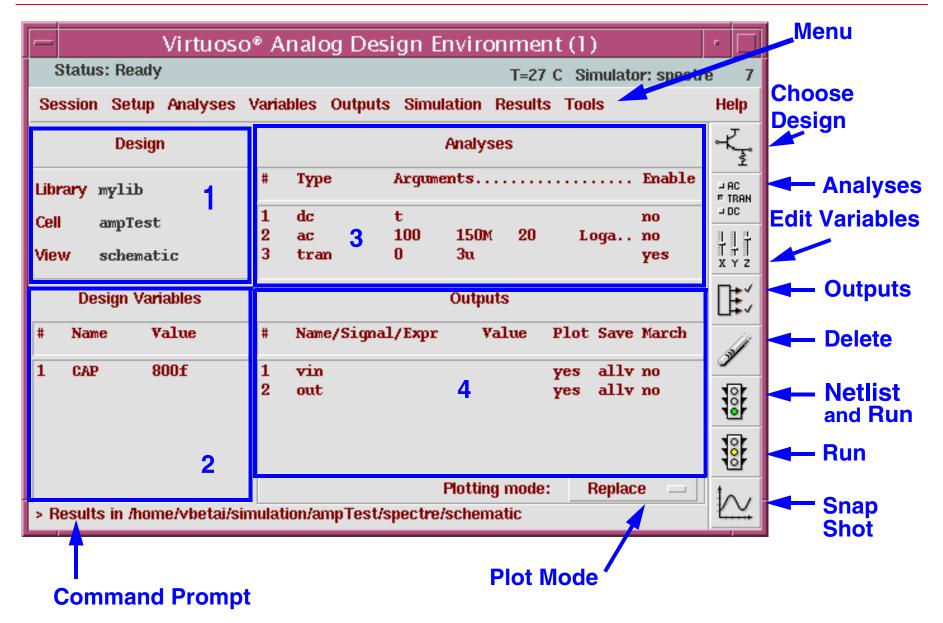

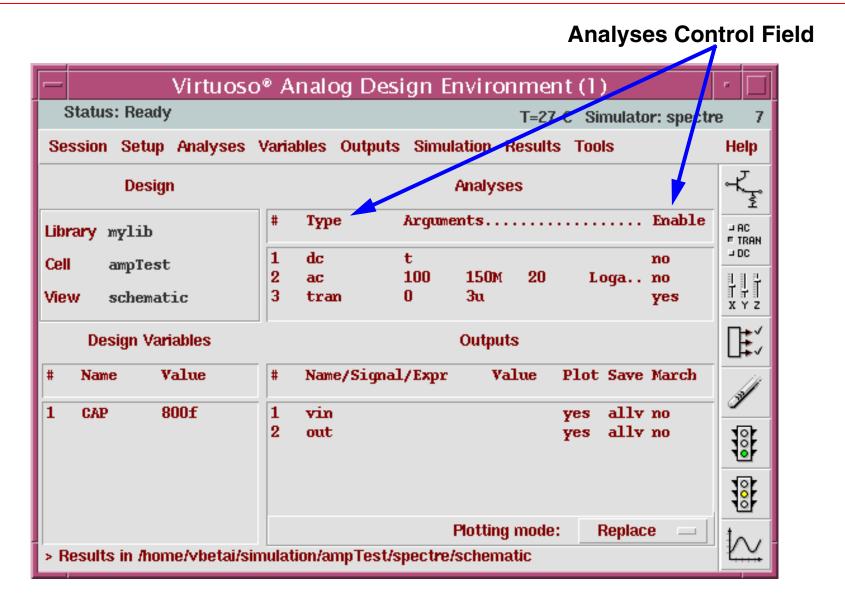

| Important Features of the Simulation Window |  |

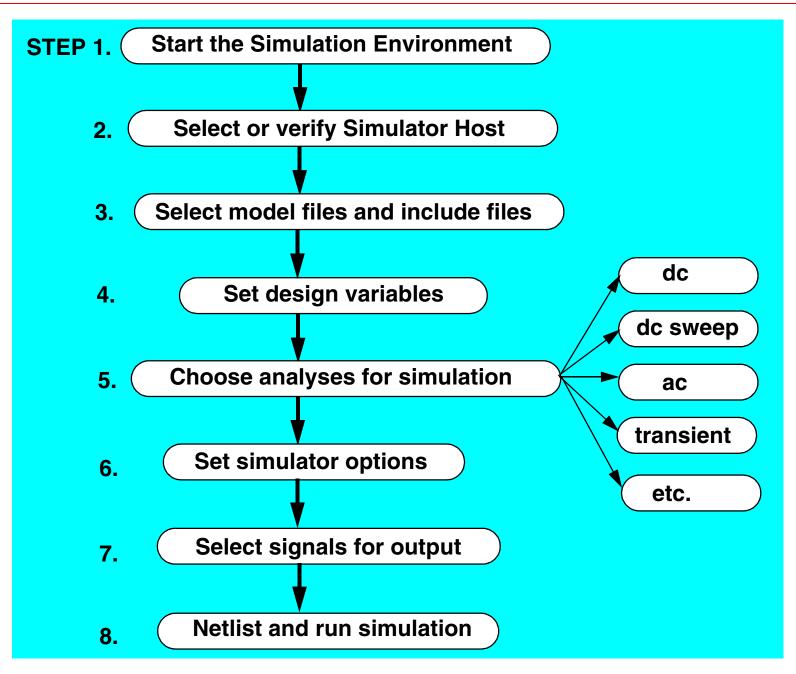

| Analog Simulation Flow                      |  |

| Starting the Simulation Environment         |  |

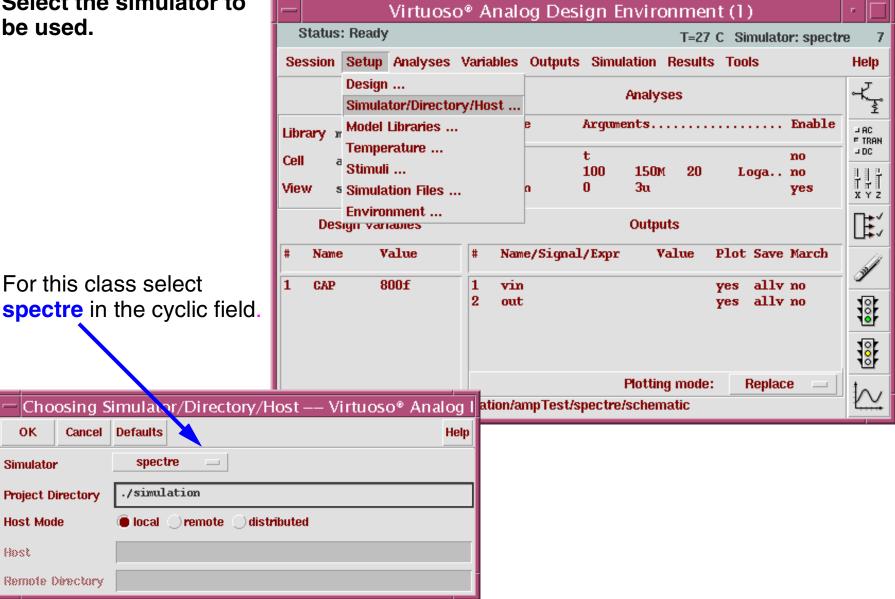

| Setting the Simulator                       |  |

| Setting the Model Libraries                 |  |

| Simulation Files                            |  |

| Setting Design Variables                    |  |

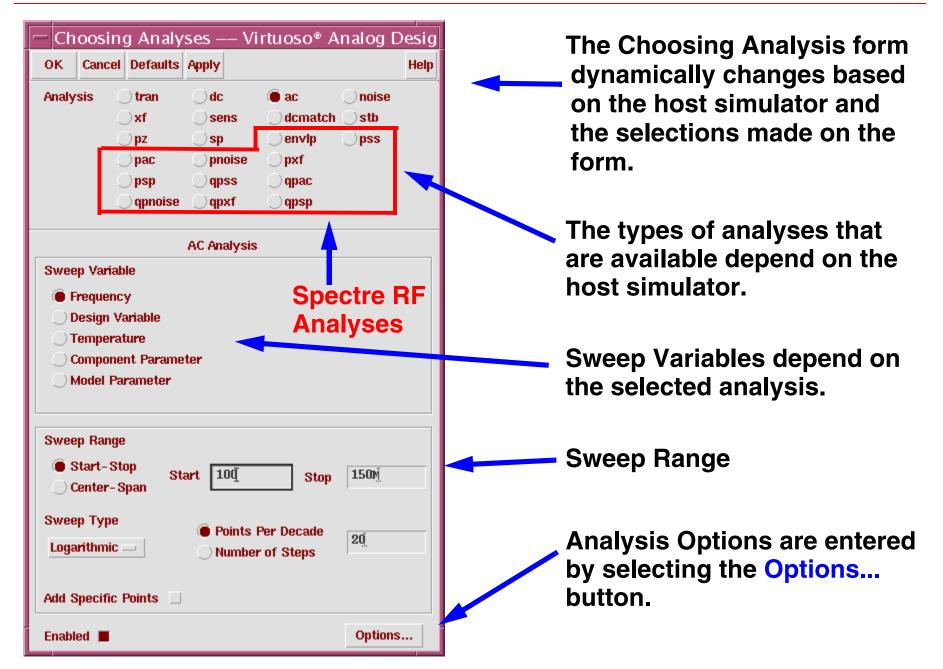

| Choosing Analyses                           |  |

| Choosing Analyses Details                   |  |

| Simulation Environment Options              |  |

| Simulator Options                           |  |

| Probing the Schematic to Save Output Data   |  |

| Reminder to Terminate Select "Outputs"      |  |

| Outputs Section of Simulation Window        |  |

| Netlisting                                  |  |

| Running the Simulation                      |  |

| Running Additional Simulations                           | 3-37 |

|----------------------------------------------------------|------|

| Control of Analyses for Simulation                       | 3-39 |

| Additional Options Using ADE                             | 3-41 |

| Analog Default Options                                   | 3-43 |

| Simulation States                                        | 3-45 |

| Stimulus Template                                        | 3-47 |

| Save Options                                             | 3-49 |

| Save Defaults and Save Session                           | 3-51 |

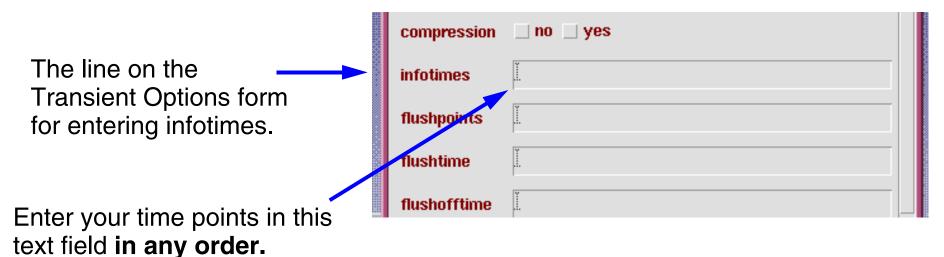

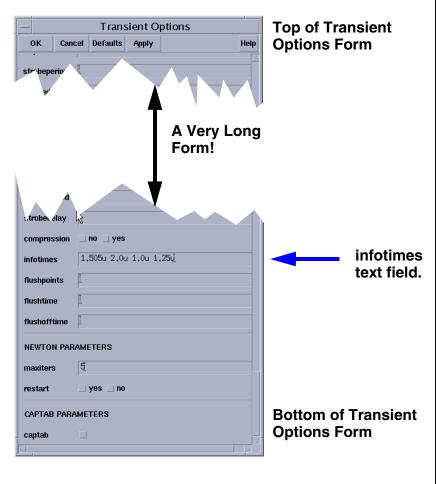

| Infotimes                                                | 3-53 |

| Infotimes Results                                        | 3-55 |

| Captab                                                   | 3-57 |

| Selecting the captab Option from ADE                     | 3-59 |

| Labs for Module 3                                        |      |

| Lab 3-1 Running Simulation                               |      |

| Starting the Simulation Environment                      |      |

| Choosing a Simulator                                     |      |

| Setting the Model Libraries                              |      |

| Choosing Analyses                                        |      |

| Setting Design Variables                                 |      |

| Notes About Find                                         |      |

| Saving Simulation Data                                   |      |

| Saving Outputs for Plotting                              | 3-9  |

| Viewing the Netlist                                      | 3-10 |

| Running the Simulation                                   | 3-11 |

| Saving the Simulator State                               | 3-12 |

| Viewing Simulation Data with Snapshot                    |      |

| Lab 3-2 Using the Stimulus Template                      | 3-16 |

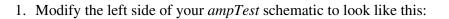

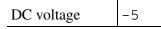

| Modifying the <i>ampTest</i> Design                      | 3-16 |

| Creating the Stimulus File                               | 3-17 |

| Running Simulation Using the Graphical Stimulus Template | 3-19 |

| Lab 3-3 Transient Operating Point Analysis, "infotimes"  | 3-23 |

| Overview of infotimes                                    | 3-23 |

| Entering the Time Points for Analysis                    | 3-25 |

| Lab 3-4 Captab                                           | 3-28 |

| Selecting the Captab Option                              | 3-28 |

### Introduction to the Analog Design Environment, Version 5.1.41

Module 1

February 10, 2005

### **Topics in this Module**

- Course objectives

- Course outline

- Class schedule

- Getting help, technical support, and documentation

- What's new in 5.1.41

- The Design Framework II design environment

- Accessing design tools

- Creating a library

- Creating cells and cell views

- Schematic capture

- Analog simulation

- Analyses

- Summary

### **Terms and Definitions**

| CDSDoc                       | Cadence® online help tool that uses a Netscape browser interface.                                       |  |  |  |

|------------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|

| CIW                          | Command interpreter window. Interface used to access DFII applications.                                 |  |  |  |

| command line                 | A line buffer in the CIW that accepts SKILL-based commands.                                             |  |  |  |

| text field                   | An area on a tool window where the user provides data.                                                  |  |  |  |

| cyclic field                 | Set of selectable options in a tool window, denoted by a small rectangle.                               |  |  |  |

| library                      | A set of design directories that includes 'cells' and 'cellviews'.                                      |  |  |  |

| Library Manager              | A Cadence tool that allows user to browse and edit a design library.                                    |  |  |  |

| Virtuoso<br>Schematic Editor | Schematic editor and symbol generation tool in DFII.                                                    |  |  |  |

| cell                         | A basic unit of a design hierarchy described by cell views.                                             |  |  |  |

| cell view                    | A specific view of a cell that includes schematic, symbol, or layout.                                   |  |  |  |

| instance                     | A uniquely named placement of a symbol onto a schematic.                                                |  |  |  |

| pin                          | A connection point on a schematic and symbol used for accessing signals.                                |  |  |  |

| bindkey                      | A predefined key on the keyboard that invokes a preselected command, sometimes called an "accelerator". |  |  |  |

### **Course Objectives**

- Learn how to create schematics, symbols, and a design hierarchy

- Set up and run analog simulations

- Analyze simulation results

- Evaluate sensitivities and mismatches to improve circuit performance.

- Run Corners, Monte Carlo, and Optimization tools to improve yield

- Create and use OCEAN scripts and SKILL to set up and run simulations

- Understand the Component Description Format (CDF)

- Create configurations with the Hierarchy Editor (HED)

- Use subcircuits and macromodels

- Run the parasitic simulation flow

- Use advanced tools to solve special problems

The objective of this class is to provide both instruction and materials on using the Virtuoso Analog Design Environment that will enable you to use the entire front-to-back design flow.

# **Getting Help**

You can get help with Cadence software from the following sources:

- Help button on forms and windows

- Cadence online documentation (CDSDoc)

- Education Services training manuals

- SourceLink® online customer support

- Customer Response Center (CRC)

### **Online Help**

Cadence reference manuals and online help files for each product are installed automatically when installing the product. Hard copies of the reference manuals are available from Cadence. All these online documents are part of the online help system, which can be accessed as follows:

- View relevant product information by clicking the help button on windows and forms. Use this information to complete a form or what can be done in the window.

- Start the CDSDoc documentation from a UNIX shell by typing cdsdoc& at the command line and search through all Cadence reference manuals and online help systems installed with each product. Also, use CDSDoc to print the reference manuals entirely or just the relevant material.

#### **Other Means of Getting Information**

- With a software maintenance agreement, subscribe to the SourceLink online support system and view known problems and solutions or communicate with other users. The SourceLink system is accessible via the internet. To open an account, send email to <u>support@cadence.com</u>.

- Training manuals, like this one, can supplement reference manuals.

- When the above information is insufficient, call the Customer Response Center.

- □ North America 1(877)CDS-4911 or 1(877)237-4911

# What's New in 5.1.41

- Spectre device checking interface

- WaveScan integration

- UltraSim integration

- Third-party OASIS integration

- Parasitic resimulation flow

### **Spectre Device Checking:**

This feature allows engineers to specify rules governing safe operating areas of devices on a primitive, a model, or an instance basis.

#### WaveScan Integration:

WaveScan is a new waveform viewing tool that is a drop-in replacement for the Analog Waveform Display (AWD) tool. WaveScan is set as the default display and provides performance and capability improvements like trace-legend visibility, X-axis parametric sweep swapping, and the ability to export graphs in **.bmp**, **tiff**, and **.png** formats.

### **UltraSim Integration:**

UltraSim is now directly integrated into ADE. UltraSim is a hierarchical simulator designed for verification of analog and mixed-signal circuits. UltraSim is not covered in this course.

#### **Third-Party OASIS integration:**

OASIS has been updated to allow third-party simulators to take advantage of Corners capability.

#### **Parametric Resimulation Flow:**

Greatly enhanced in 5.1.41, the parametric resimulation flow has been rewritten to improve usability and limit previous restrictions concerning Assura. You may now backannotate both node voltages and device operating points onto schematics. New capability for parasitic resistance annotation has been added as well.

### **Overview of Virtuoso Analog Design Environment**

The Virtuoso Analog Design Environment is a software tool set within Design Framework II that is used to set up and run analog simulations. The Virtuoso Analog Design Environment also accesses and views the simulation results.

The Virtuoso Analog Design Environment allows you to:

- Choose the simulator host

- Choose the type of analysis: ac, dc, transient, parametric, sensitivity, etc.

- Set design variables: Vdd, frequency, Cout, etc.

- Append model files and include files

- Netlist and run simulations

- Quickly alter the simulation setup and rerun the simulation

- Plot simulation results in the Waveform display tool

- Evaluate simulation results using waveform expressions

- Run multiple simulation tools: Corners, Monte Carlo, Optimizer, etc.

- Automatically set up, save, and run OCEAN scripts

The Virtuoso Analog Design Environment is a set of software design tools used to set up, control, and run circuit simulations. ADE allows you to choose the simulator host, set design variables, select model files, and to select analyses to add, modify, or delete from next simulation run.

The Virtuoso Analog Design Environment provides a user-friendly graphical interface that includes pull-down menus and icons for making fast and easy changes and also provides control for accessing the simulation results and displaying the results to the waveform display tool. The results can be entered into other tools for waveform processing or to obtain specific data using expressions.

The Virtuoso Analog Design Environment provides access to multiple simulation tools like Corners, Monte Carlo, and the Circuit Optimizer. ADE also allows you to automatically set up, save, and run OCEAN scripts.

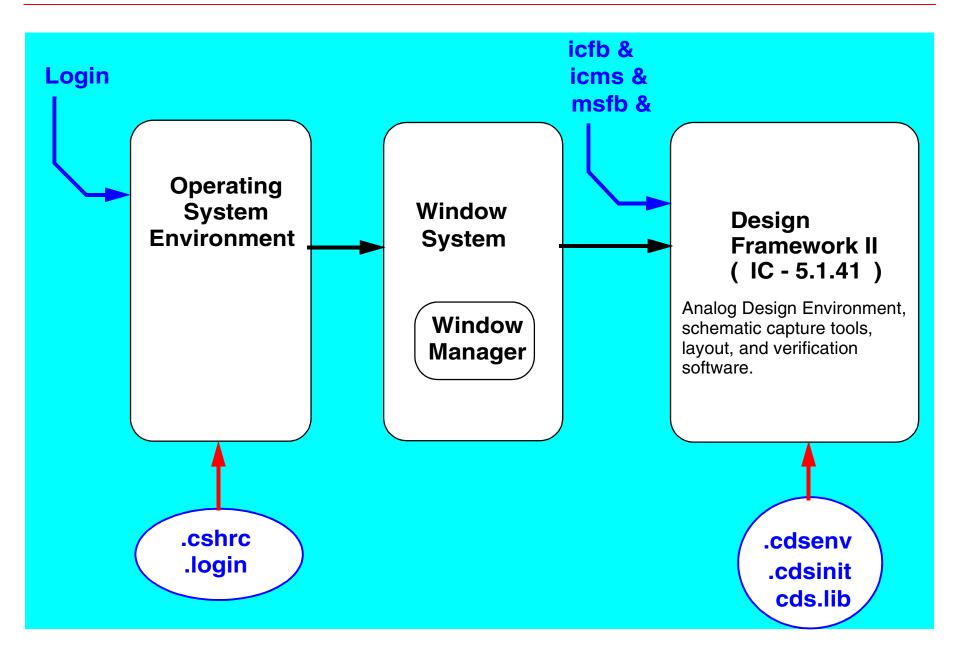

### **Design System Initialization Files**

There are some design system initialization files that configure the operating system environment. For example, the *.cshrc* and *.login* files configure the UNIX environment when you log in and start a UNIX application.

The initialization file, *.cdsinit*, customizes the Virtuoso Analog Design Environment. The *cds.lib* file sets the paths to the libraries. These files, along with the *.cdsenv* file, are discussed later.

For more information on configuring your operating system environment for the Virtuoso Analog Design Environment, consult the *Cadence Design Framework II Configuration Information* guide.

### **Overview of the Design Framework II Environment**

Introduction to the Analog Design Environment, Version 5.1.41

The Virtuoso Analog Design Environment is a set of design tools that operate within Design Framework II. Design Framework II is the underlying structure for Cadence design tools for schematic capture, analog simulation, and layout. It provides a single integrated environment for accessing all tools and design data, including the ability to:

- Access to the Command Interrupter Window (CIW) using *icfb*, *icms*, or *msfb*.

- Use the Library Manager Tool to browse design libraries and open cell views.

- Create new libraries, cells, and cell views.

- Start or edit a schematic view or symbol view.

- Start or edit a layout design.

- Run layout verification.

- Start the Virtuoso Analog Design Environment and run simulations.

- Access simulation results directly using the Results Browser.

- Run OCEAN scripts.

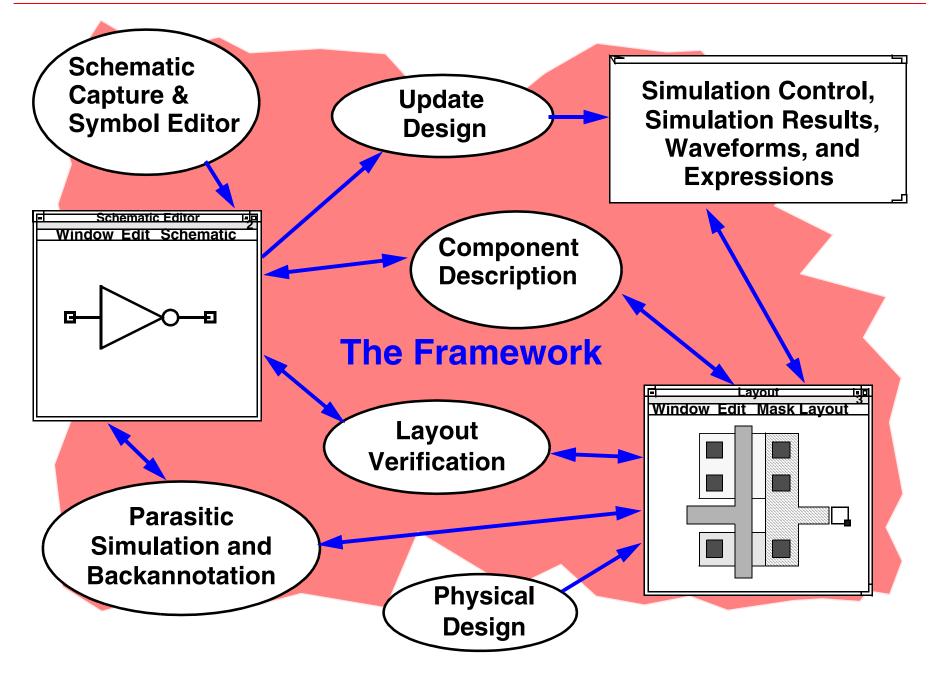

### **Advantages of Using Design Framework II**

- Common software environment for using schematic capture, simulation, layout, and design verification

- Easy-to-learn, consistent user interface

- Similar appearance between most forms and windows

- Communication between software tools within the DFII environment

- Tool windows remain open while running other applications

- Data can be "backannotated"

- From layout to schematic

- **From simulation to schematic**

- From simulation to layout

- Applications may be customized or automated using SKILL or the OCEAN command language

The Cadence Design Framework II environment is an integrated design environment. An integrated environment means that numerous tools and applications operate together. For Design Framework II the environment provides schematic capture, simulation control, netlist generator, circuit simulator, waveform display, layout and verification tools.

For the design software tools, DFII provides:

Consistent user interface

Analog applications in the design framework have the same "look and feel." Menu items are often in the same place in every application.

#### Consistent database

A consistent database stores all design information. Tools share data in real time so long formalized translations between tools are not needed. The DFII environment also saves time during schematic to layout verification, because it updates layout geometries as the schematic component parameters change.

#### Cooperating tools

Applications run concurrently, with results available to all other tools, eliminating the need to open and close applications when changing tool contexts. For example, update and simulate a schematic without restarting the simulation environment. Updates are known to the simulation window as soon as they are made in the schematic entry window.

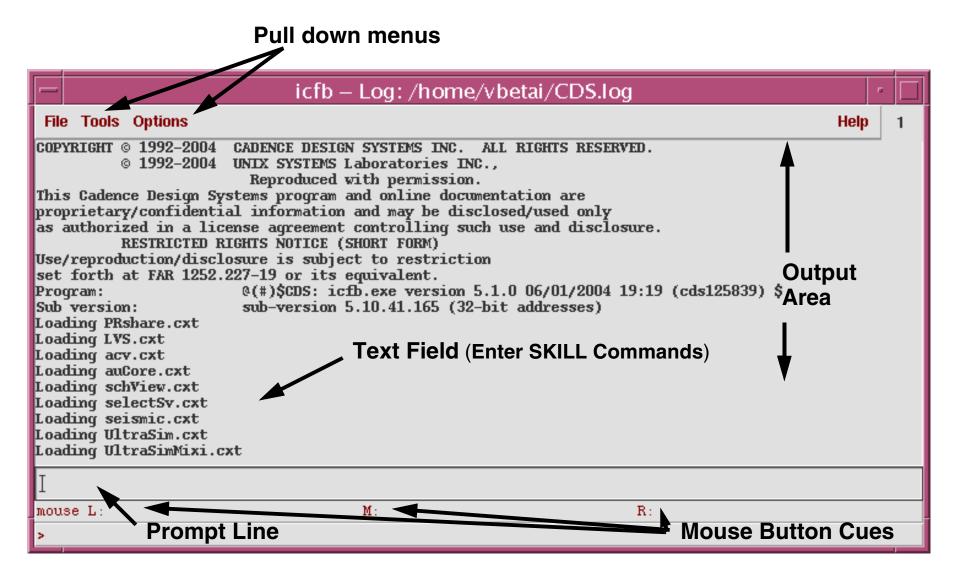

## The Command Interpreter Window (CIW)

### Enter: *icfb &, icms &, or msfb &*

The Command Interpreter Window (CIW) is at the heart of the framework system. Use this window to access framework-based applications. System and error messages from applications are reported in this window.

### Output Area

The output area displays a running history of the commands used with their results. For example, it issues a status message when a cell library is opened. This data is saved in the *Log File* whose path appears as the application title of the CIW. Use scroll bars to view previous output pane data without having to resize the CIW.

### Text Entry Field

Enter Cadence SKILL commands in this area. Every pull-down menu command in the Design Framework II environment has an equivalent SKILL command. Advanced users can define and execute their own SKILL commands by entering them here.

#### Prompt Line

The prompt line at the bottom of the CIW indicates the next step when carrying out a command executed in any Design Framework II application window.

#### Mouse Button Cues

Tells which mouse button to push to execute a command in a Design Framework II window.

## Using a Form

| A Sample Form |                         |       |               |              |                |

|---------------|-------------------------|-------|---------------|--------------|----------------|

| ОК            | Cancel Defaults         | Apply |               | Help         |                |

| Templa        | Template File Load Save |       |               |              |                |

|               |                         | Lib   | orary Browser | ]            |                |

| Run Dir       | rectory                 | •     |               |              |                |

| Library Name  |                         |       | assLib        |              |                |

| Top Ce        | ll Name                 |       |               |              |                |

| View Name     |                         |       | x2            |              |                |

| Output File   |                         |       | layout        |              |                |

| Output        |                         | ♦ S   | tream DB      | ♦ ASCII Dump |                |

| Show M        | lessages                |       |               |              | └── Text entry |

| Library       | Version                 | 5.    | 1 🖵           |              | area           |

|               | Toggle Buttor           |       | clic Field    |              | Radio Buttor   |

Forms provide a place to enter the information required by a command.

The top of the form has a *title bar* and a set of *banner buttons*. The body of the form contains *prompts* that indicate which option is being set. Next to the prompt is one of the following:

- *radio button*, for choosing one of several options

- *text entry area*, for typing information

- *toggle button*, for turning options on or off

- *cyclic field*, for choosing one of many options. Initially only one option is shown. Move the pointer to the field and hold down the left mouse button, the other options appear.

The form might also have buttons such as *Browse*, which shows a browser window, or *More Options*, which displays another form.

Change of an entry on a form is disabled when the name appears in gray instead of black, and the text entry area is shaded.

- Press the **Tab** key or mouse to move to the next text entry field.

- Use the left and right arrows on the keyboard to move the cursor in a text entry field.

Press **Control-a** to go to the beginning of a line; **Control-e** to go to the end of a line; **Control-u** to erase to the beginning of a line.

### **Initializing the Design Framework II Environment**

The Design Framework II software reads your *.cdsinit* file at startup to set up your environment. The *.cdsinit* file:

- Sets user-defined bindkeys when the Design Framework II environment is started.

- Redefines system-wide defaults.

- Contains SKILL commands.

The search order for the .cdsinit file is:

- <install\_dir>/tools/dfll/local

- the current directory

- the home directory

Here is the path to a sample .cdsinit file:

<install\_dir>/tools/dfII/samples/artist/cdsinit

Start the Design Framework II environment, it reads the *.cdsinit* file to set up your configuration. The search order for the *.cdsinit* file is *<install\_dir>/tools/dfII/local*, the current directory, and finally the home directory. When a *.cdsinit* file is found, the search stops unless a command in a *.cdsinit* file reads other user files.

The *.cdsinit* file is a text file written in SKILL. A statement in a *.cdsinit* file can load user-defined bindkeys. Another statement might set Waveform Window defaults.

A sample *.cdsinit* file included with the software contains examples of statements to copy into your own *.cdsinit* files. It has very detailed comments about command usage. This sample is located at *<install\_dir>/tools/dfII/cdsuser/.cdsinit*. An additional sample *.cdsinit* file exists for analog designers at *<install\_dir>/tools/dfII/samples/artist/cdsinit*.

#### **The Installation Path**

The Design Framework II software product hierarchy is discussed in detail in the *Cadence Design Framework II Configuration Information* guide.

## **IC Design Flow, Front to Back**

Introduction to the Analog Design Environment, Version 5.1.41

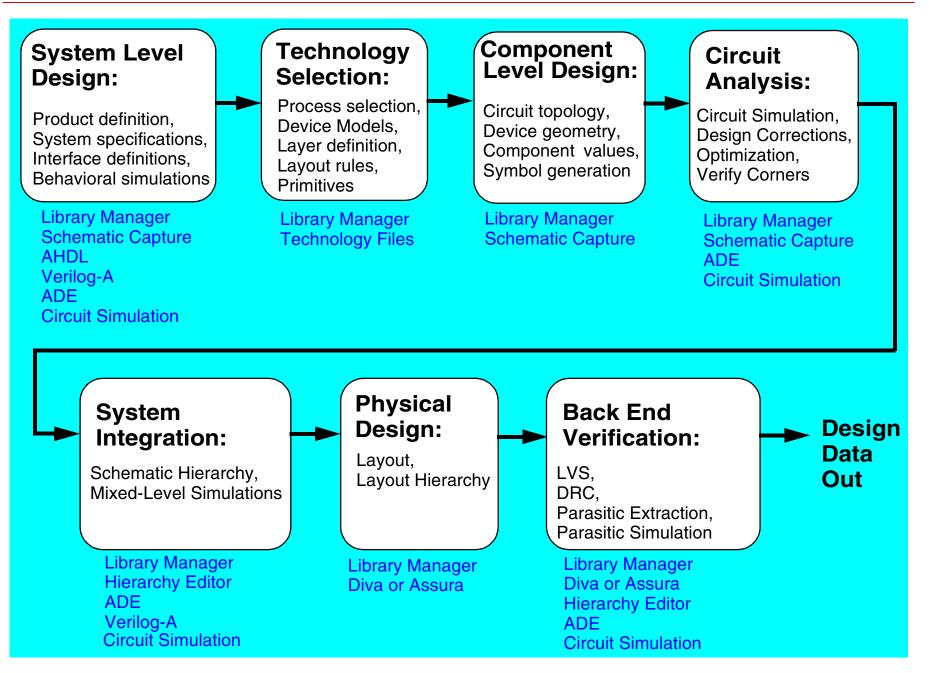

The graphical flow above shows a Front to Back design flow for integrated circuits or related system design. The blocks show the major steps or design categories. The text below each block shows the software tools used in the corresponding design steps.

- At the front end, the product, device or system is defined. The system-level specifications are used for behavioral simulation of the system.

- A fabrication process or technology is selected.

- A schematic of a specific block is captured.

- The design of the circuit is simulated. If needed, the circuit is redesigned to achieve specified goals.

- The circuit is integrated into a hierarchy. The hierarchy is then simulated.

- Physical design or layout capture of the circuit is completed. The layout of the hierarchy is then completed.

- Back end verification of the layout includes design rule checks, layout versus schematic checks, and parasitic extraction. The extracted parasitics are "backannotated" to the schematic for parasitic simulation using the circuit simulation software.

### **The Library Manager**

#### The Library Manager is a graphical data management tool.

Introduction to the Analog Design Environment, Version 5.1.41

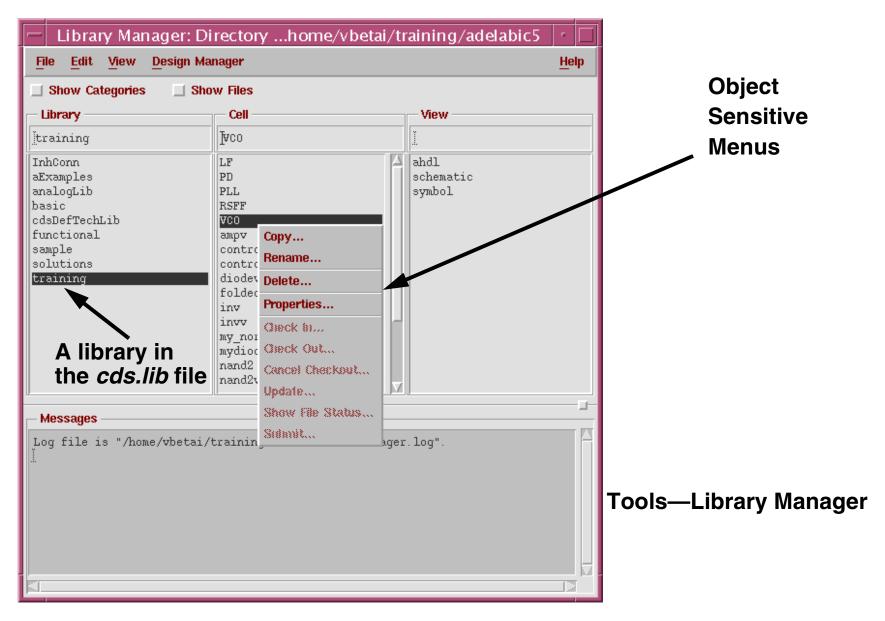

The Library Manager provides a convenient way to browse libraries containing cells and cell views. The most common use is to display the contents of libraries graphically. Other functionality includes renaming, copying, specifying permissions for, creating categories for, deleting, and viewing properties of design data. Use the Library Manager to create cells and views, to edit or read a design, and to access the design manager.

The illustration above shows a fully expanded library. Initially, the Library Manager lists only the library names that are set in the *cds.lib* file. This file contains the paths to the libraries used in the design session, including example libraries provided by Cadence, such as *analogLib* and *basic*.

Expand design data with Object Sensitive Menus (OSM) or with the mouse. To expand data, point at the word that represents the data in the Library Manager and choose the appropriate mouse button or menu command.

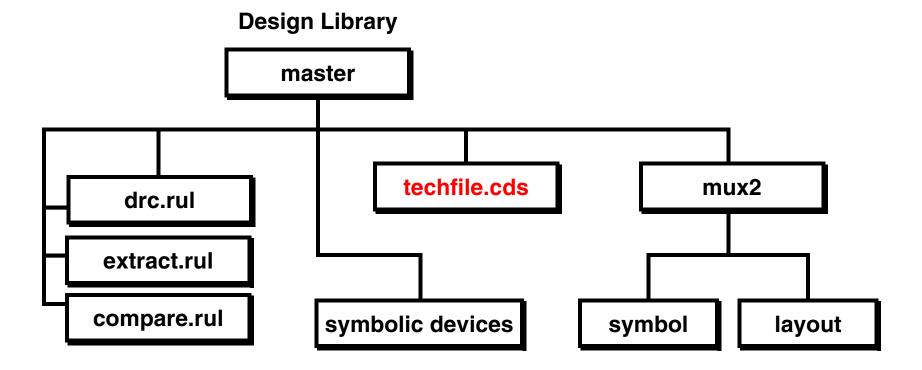

### **The Library Structure**

#### Introduction to the Analog Design Environment, Version 5.1.41

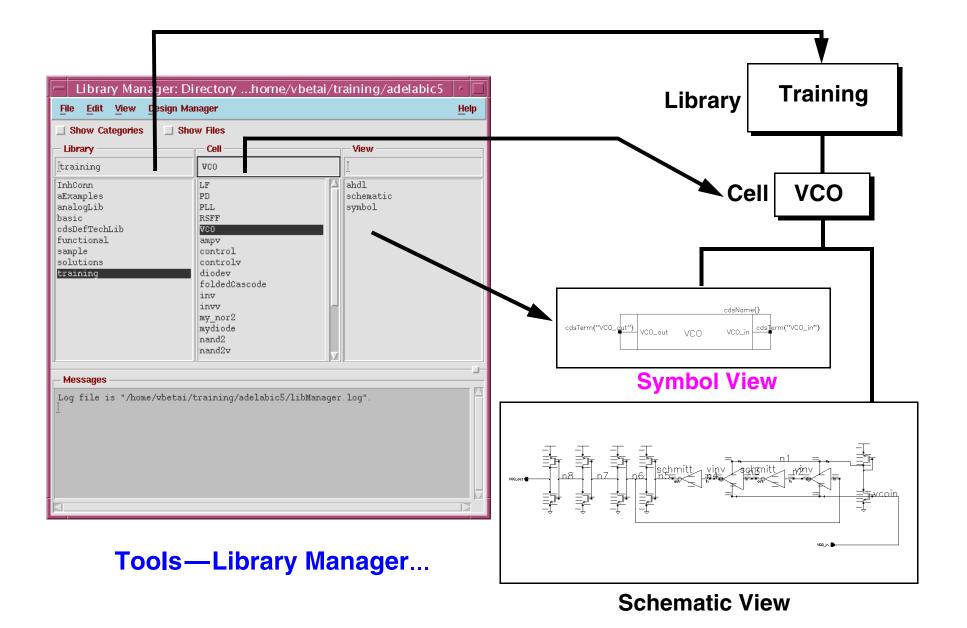

Library

A *library* is a collection of cells. The library also contains all the different views associated with each of the cells. **Reference** libraries typically contain well-characterized cells that can be instantiated in many different designs. Examples are the *analogLib* and *basic* libraries. **Design** libraries contain cells currently under development by a particular user, group, or for a particular design project.

#### Cells

A *cell* is a logical component in your library. It can be a building block such as a *VCO* or *amplifier*. It can also be the top level chip name.

#### Views

A *view* is a particular representation of a cell such as a *layout*, *symbol*, or *schematic*. An application tool, such as *Virtuoso Schematic Editor*, creates a view. Although a chip can include many levels of cell hierarchy, none of the hierarchical complexity is reflected in the libraries.

A library is a flat collection of cells. Details of the design hierarchy exist inside the views that contain instances of other cells. The library treats all cells the same.

# **Creating a New Library**

### In the CIW or the Library Manager, select File-New-Library.

| OK       Cancel       Defaults       Apply       Help         Library       Technology File       If you will be creating mask layout or other physical data in this library, you will need a technology file. If you plan to use only schematic or HDL data, a technology file is not required.         NDL lab       MDL labtest       Ocmpile a new techfile         MDL labtest       Compile a new techfile       Ocmpile a technology file                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                  |             |          | Ne    | ∧ Library       |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------|----------|-------|-----------------|------|

| Name       mylil         Directory (non-library directories)       If you will be creating mask layout or other physical data in this library, you will need a technology file. If you plan to use only schematic or HDL data, a technology file is not required.         NDL lab       MDL labtest         MOL lab       Implementation         MOL lab       Implementation         Models       Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ок                                                               | Cancel      | Defaults | Apply |                 | Help |

| Name       Image: | Library                                                          |             |          |       | Technology File |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Director<br><br>CORNER<br>CSurf<br>MDL lab<br>MDL lab<br>MOL lab | you<br>plan |          |       |                 |      |

- Specify the library name and path.

- Specify the design manager to use.

- For Physical Design and Verification, specify the ASCII technology file or technology file library to be attached to the new library.

The new library is entered into the *cds.lib* file.

Introduction to the Analog Design Environment, Version 5.1.41

When creating library, use a form to specify the library name and path, the design manager to use, and the technology file to attach to the library.

Technology File Contents

The *technology file* is a large data file that specifies all of the technology-dependent parameters associated with that particular library. Design rules, symbolic device definitions, and parasitic values are some of the technology-specific parameters common to all cells in a library.

*cds.lib* File

The software automatically updates the *cds.lib* file when creating a library through the CIW's **File**—**New**—**Library** command, when copying one library to another name, or renaming a library. This file contains the paths to all of the libraries used in the design session, and can be accessed through CIW's **Tools**—**Library Path Editor** command.

# **Shared Technology Library**

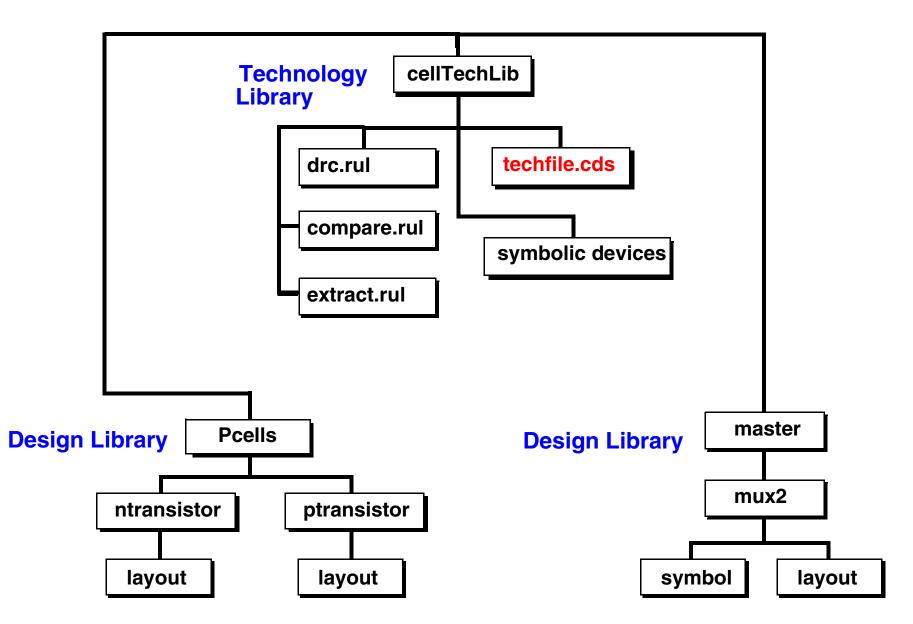

This example shows several libraries sharing the same technology file library.

Introduction to the Analog Design Environment, Version 5.1.41

Share technology file information between different libraries. Create a technology file library and attach your design libraries to the technology file library. Use the **Technology File—Attach To** command in the CIW to attach the design library to the technology file library. Sharing a technology file library with other libraries will share the same Assura<sup>®</sup> rules, layer information, and symbolic devices amongst a group of libraries. Sharing a technology file can help reduce the size of the design libraries, because the technology information is stored at only one location.

### *techfile.cds* file

The *techfile.cds* file contains the binary technology file. This file name must be called *techfile.cds*.

Assura Rules

The Assura rules are stored as separate ASCII files. For each type of rule (DRC, Extract, and Compare), there is an Assura rules file.

### Symbolic Devices

The symbolic devices such as contacts, pins, transistors, and wire information can be shared between libraries.

# **Technology File Stored in the Design Library**

This example shows a technology file being stored inside a design library and not being shared with other libraries.

Introduction to the Analog Design Environment, Version 5.1.41

A library can have its own technology file information that is stored inside of the library.

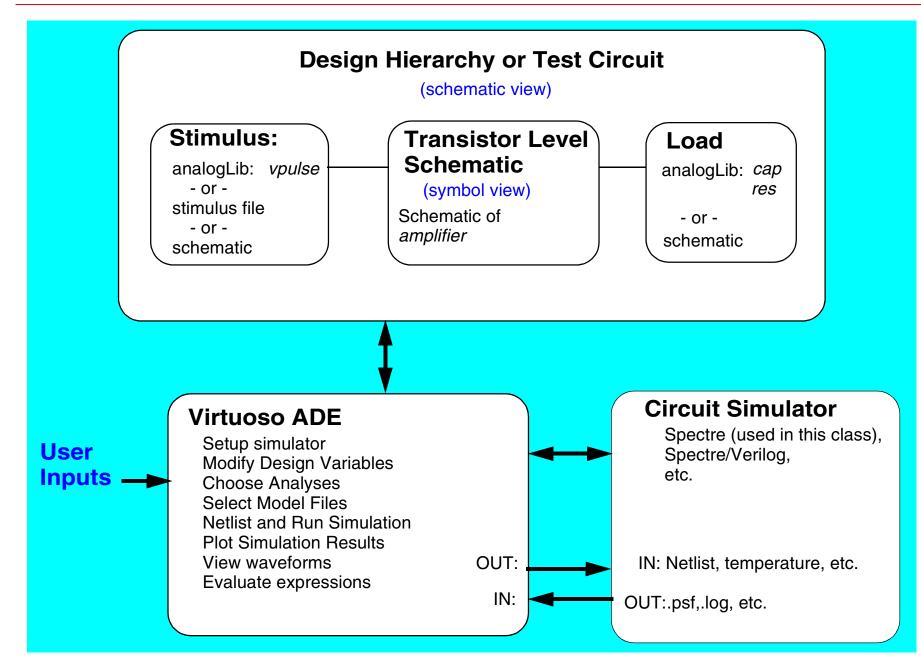

# **Overview of Circuit Simulation**

Introduction to the Analog Design Environment, Version 5.1.41

The block diagram above shows an overview of the circuit simulation process.

- The circuit schematic is captured or edited.

- A symbol of the schematic is placed in a hierarchy or test circuit schematic.

- The Virtuoso Analog Design Environment is started.

- The user provides input to the Virtuoso Analog Design Environment to set up and control what information is netlisted and then sent to the circuit simulator.

- The user used the Virtuoso Analog Design Environment to run the circuit simulator.

- The user selects the information to be printed, plotted, or to be analyzed.

- The user modifies the setup or edits the schematic for the next simulation.

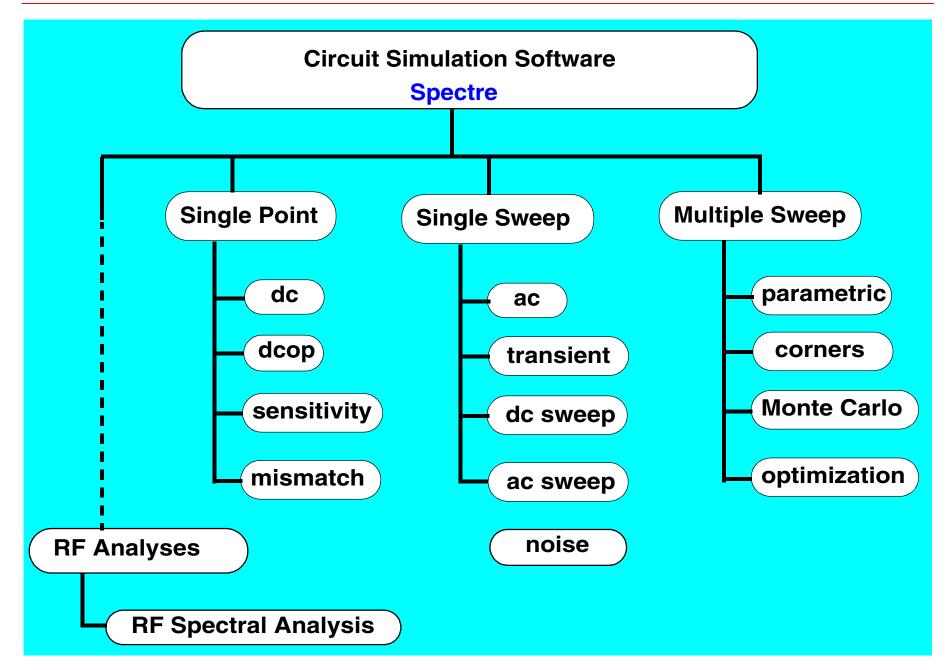

# **Types of Circuit Simulation Analyses**

Introduction to the Analog Design Environment, Version 5.1.41

The diagram shows the variety of analyses available with analog circuit simulation.

Single-point analyses often include the steady state **dc** solution of the circuit. The operating point **dcop** solves the operating point device parameters and low frequency gain of the circuit.

Single-sweep analyses often include **ac** and **transient** analysis. The **ac** analysis is a frequency sweep of the circuit. The **transient** analysis is a time sweep of the circuit operation to a time domain stimulus. A **dc sweep** analysis is a multiple point dc analysis performed while stepping a parameter such as temperature, design variable, or a model parameter. Solving the dc gain of an amplifier as a function of temperature is often called a **temperature sweep**. Solving the gain of an amplifier as a function of a model parameter is called a parametric sweep. It is also possible to sweep the **ac** gain of an amplifier at a specified frequency of the amplifier over temperature. This is called an **ac temperature sweep**.

Multiple sweep analyses refer to sweeping one variable and then stepping another variable between successive sweeps. In **parametric** analysis, the two or more variables are altered at specified intervals. In the **Corners** analysis, variables are specified at named corners. In the **Monte Carlo** analysis, the parameters are altered using random number generators and a specified distribution. In **optimization** analysis, the parameter are altered using the results of the previous simulation and a search algorithm.

The Virtuoso Analog Design Environment and the Spectre circuit simulator are capable of performing the analyses shown above. In addition, the Spectre circuit simulator can perform special steady state **ac spectral analysis** on RF waveforms. These analyses are discussed in the Spectre RF classes.

# Summary

In this module we discussed:

- Course objectives

- Getting Help, including CDSDoc

- Design Framework II environment

- Using forms

- Creating a library

- Creating cells and cell views

- Overview of schematic capture

- Overview of circuit simulation in the Virtuoso Analog Design Environment

- Types of simulation analyses

In this module we provided an introduction to the class, including:

Class objectives

Online documentation

This module also provided discussion on the Design Framework II environment, including:

- Starting DFII with *icfb*, *icms*, or *msfb*.

- The Command Interpreter Window (CIW)

- Use of forms

- Front to Back design flow using Design Framework II

- Overview of schematic capture

- Overview of circuit simulation in the Virtuoso Analog Design Environment

- Types of simulation analyses

Introduction to the Analog Design Environment, Version 5.1.41

# Labs for Module 1

## Introduction

| -                                 | CDSDoc: Library                                                                                                                                                                                                                                                                                                                                                                                       | •            |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| <u>F</u> ile                      | e <u>E</u> dit ⊻iew                                                                                                                                                                                                                                                                                                                                                                                   | <u>H</u> elp |

|                                   | Active Library:<br>C5.1.41 /glawson/gary/IC5141                                                                                                                                                                                                                                                                                                                                                       | 4            |

| C                                 | Docs by Product 🛛 🗸                                                                                                                                                                                                                                                                                                                                                                                   |              |

| 计算计算计 化不能不能不能不能不能不能不能不能不能不能不能不能不能 | <ul> <li>Dracula</li> <li>HyperExtract</li> <li>Install and License</li> <li>Languages</li> <li>PKS</li> <li>Pearl</li> <li>SKILL</li> <li>Silicon Ensemble - DSM</li> <li>Silicon Ensemble - SI</li> <li>Silicon Ensemble - Ultra</li> <li>Spectre</li> <li>Spectre RF</li> <li>Timing Library Format</li> <li>Virtuoso Composer</li> <li>Virtuoso Layout Editor</li> <li>Virtuoso Placer</li> </ul> |              |

|                                   | Search Open Exit He                                                                                                                                                                                                                                                                                                                                                                                   | lp           |

| Γ                                 |                                                                                                                                                                                                                                                                                                                                                                                                       |              |

### Lab 1-1 Setting Up the Database

### Objective: To download and set up the course database.

- 1. Click the <u>ADE 5 1 41.tar.Z</u> link and download the compressed file to your home directory.

- **Note:** You can put the database where you like, but these instructions assume your home directory is the destination for the database.

- 2. After downloading the database file, you must uncompress it using the following command:

uncompress ADE\_5\_1\_41.tar.Z

After you uncompress the course database file, you will have a tar file called  $ADE_5_1_41.tar$ .

3. Extract the *.tar* file by entering the following command in the window:

tar xvf ADE\_5\_1\_41.tar

This command creates a directory called adelabic5.

4. You can now remove your tar file by entering:

rm  $ADE_5_1_41.tar$

5. Make sure that you read the *README* file in the *ADE* directory concerning the versions of the software to use with these labs.

### Lab 1-2 Getting Started

### Objective: To login, start a shell tool, and use CDSDoc.

This lab activity is intended to help you begin using the Design Framework II design tools. You need to be familiar with the workstation and the operating system you will be working with.

This class was developed using the Solaris 2.8 operating system. If your operating system is different, your instructor or system administrator may provide additional instructions.

- 1. In a terminal window, type csh at the command prompt to invoke the C shell.

- 2. To verify that the path to the software is properly set in the .cshrc file, open a terminal window and enter:

- > which icms

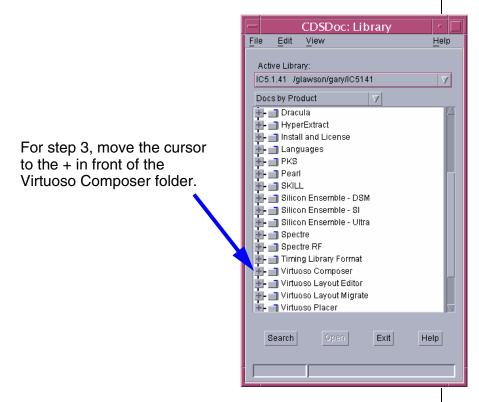

### Starting the Online Help, CDSDoc

1. In the UNIX window enter the command:

> cdsdoc &

2. The CDSDoc: Library window should appear.

This is a graphical interface for selecting topics from the online documentation tool.

3. With the mouse, position the cursor on the + symbol in front of the **Virtuoso Composer** folder, and click **left**.

The Composer folder expands to show available topics.

4. Click **left** in the subtopic field.

The Virtuoso Composer User Guide appears.

- 5. Activate the selected topic with a left click on the open button.

- 6. After briefly viewing the information displayed, close the browser. Then click the **Exit** button on the **CDSDoc: Library** window.

The Cadence online documentation is available even without starting the Cadence design software. If the software is installed, you can access the documentation from any terminal window operating in a C shell with a path to the installation by typing cdsdoc at the command prompt.

### Starting the Cadence Software

You will use the installed database to do your work.

- 1. Change to the course directory by entering this command:

- > cd ~/adelabic5

You will start the Cadence Design Framework II environment from this directory because it contains cds.lib, which is the local initialization file. The library search paths are defined in this file.

If you start the Design Framework environment from another location, you will have to perform additional steps to access the training libraries.

- 2. In the same terminal window, enter:

- > icms &

The Command Interpreter Window (CIW) appears at the bottom of the screen.

- 3. If the "What's New ..." window appears, close it with the **File—Close** command.

- 4. Iconify other windows that are open at this time and make sure that the CIW is visible.

### Lab 1-3 Top-Down System Modeling

# Objective: To simulate a block-level design that uses AHDL modules.

In this first lab, you will simulate a top-down, block-level design. Assume that a design specification has been given to you, and you have used AHDL (analog behavioral) modules using the Verilog®-A language to describe the functions of your blocks.

The design is a peak detector circuit, which is already set up for you in a testbench for simulation. In this lab, you will run the simulation on this block-level design. For the rest of the course, you will then build the individual blocks that characterize the system, following the logical steps of a design flow.

This lab will give you a brief introduction to the simulation environment. You will learn about the simulation environment in great detail in the following modules.

### **Design Flow**

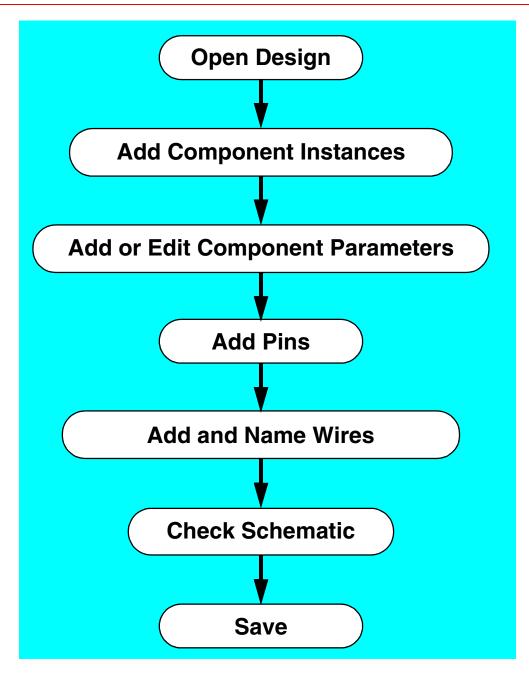

The Design Flow diagram below represents the steps that will be taken in the front-to-back analog design methodology in this class. The current block is highlighted to indicate where you are in the flow.

### **Opening the Peak Detector Circuit**

1. In the CIW, execute **Tools—Library Manager**.

The Library Manager appears.

2. In the Library Manager, click **left** to expand the *training* library and the cell named *peakTestv* ("v" is for Verilog-A).

Only a *schematic* view exists for this cell.

**Note:** All of the Verilog-A descriptions used in the modules in the *peakDetectv* design came from the Cadence hierarchy. They are included with your software installation.

3. With your **middle** mouse button, activate the Object Sensitive Menu (OSM) over the word *schematic* in the View section and select **Open**.

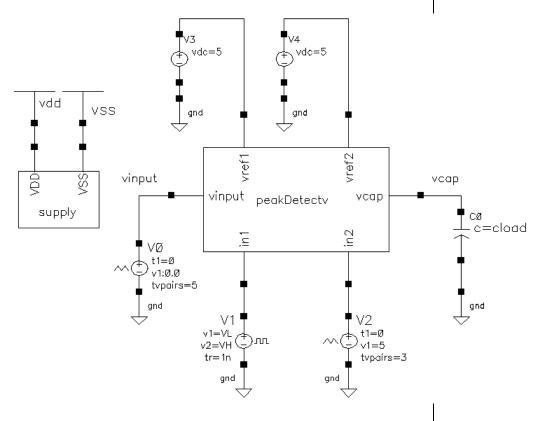

The schematic of the testbench with supplies and stimuli for a peak detector circuit appears.

4. Run your cursor over the *peakDetectv* block until a rectangular box is highlighted around it. Click **left** to select the *peakDetectv* block, and the box will go from dashed lines to solid.

### 5. Execute Design—Hierarchy—Descend Edit.

Tip: You can also press the E (Shift E) key.

6. In the Descend form that appears, set the View Name to schematic, and click **OK**.

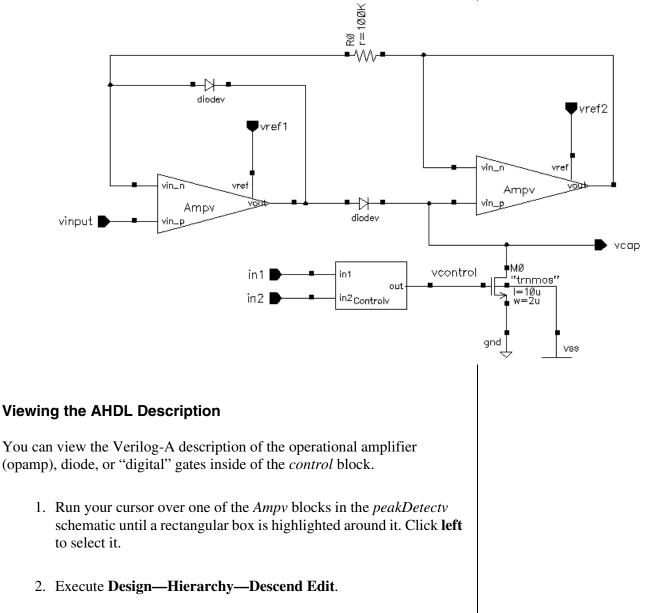

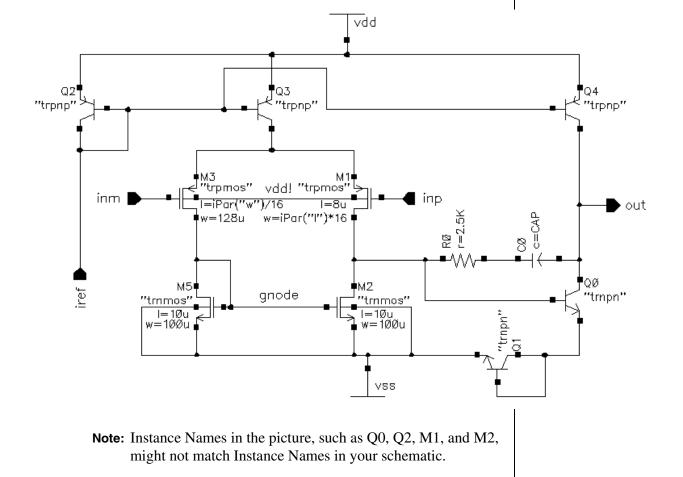

The *peakDetectv* schematic appears. You will study this design throughout the course. It consists of two operational amplifiers, two diodes, an NMOS transistor, and a resistor. All of the components except the resistor and NMOS device are modeled with Verilog-A, an analog HDL language.

Using the Verilog-A language supports the top-down design methodology.

**Tip:** You can also press the  $\mathbf{E}$  (Shift E) key.

3. In the Descend form that appears, set the View Name to **veriloga** and click **OK**.

A text window appears.

4. Put your cursor in the window, and press Return.

The Verilog-A description of the opamp, called *ampv*, appears. Study the file and see if you can understand the behavior and structure of this description.

5. After viewing the file, exit the editor: For the vi editor, enter:

If you have used the Text Editor tool provided by the Common Desktop Environment (CDE), execute **File—Close**.

6. View the *veriloga* descriptions of the diode and logic gates if time permits.

### **Running Simulation**

You will set up and run a simulation. You will learn more about the specifics of the simulation environment in the next section.

1. In the schematic window, execute Tools—Analog Environment.

In a few moments, the Virtuoso Analog Design Environment simulation window appears, and the *peakTestv* schematic is in view again.

### **Choosing a Simulator**

You will set the simulator to run the Spectre<sup>®</sup> tool, a high-speed, highly accurate analog simulator that is integrated directly into the Virtuoso Analog Design Environment.

- 1. In the Simulation window, execute **Setup—Simulator/Directory/Host**.

- 2. In the Choosing Simulator form, set the Simulator field to **spectre** and click **OK**.

Lab 1-3

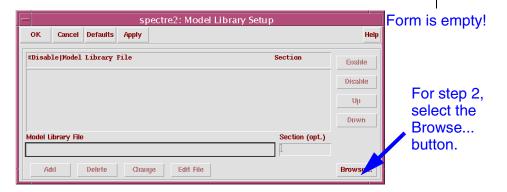

#### Setting the Model Libraries

The Model Library File contains the models needed for simulation. For this simulation, the NMOS device in the *peakDetectv* design is the only one that is used.

1. Execute Setup—Model Libraries.

The Models Library Setup form appears.

2. Place your cursor in the Model Library File field and enter the following value:

~/adelabic5/Models/myModels.scs

3. Click Add.

The path moves to the Model Library File field. This file will now be included in the simulation environment and used to describe the NMOS transistor in the *peakDetectv* circuit.

4. Click **OK** in the Setting Model Path form.

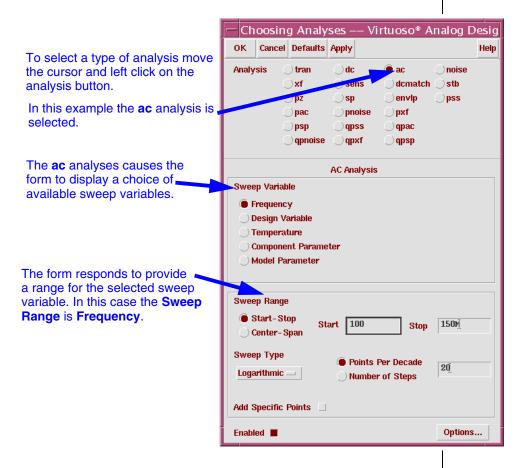

### **Choosing Analyses**

You will run a transient analysis on the *peakTestv* design.

1. In the Simulation window, click the Choose Analyses icon.

Tip: You can also execute Analyses—Choose.

The Choosing Analyses form appears.

2. To set up for Transient Analysis:

a. In the Analysis section, select **tran**.

- b. Set the Stop Time field to **390u**.

- c. Select Moderate as the errpreset.

- d. Turn **On** the Enable button.

e. Click OK in the Choosing Analyses form.

| - Choosing Analyses Virtuoso® Analog Desig |        |                             |                     |                           |      |

|--------------------------------------------|--------|-----------------------------|---------------------|---------------------------|------|

| ок                                         | Cancel | Defaults                    | Apply               |                           | Help |

| Analy                                      | ŝ      | ) tran<br>) xf<br>) pz      | ⊖dc<br>⊖sens<br>⊖sp | ⊖ac<br>⊖dcmatch<br>⊖envlp | Östb |

|                                            | Ğ      | ) pac<br>) psp<br>) qpnoise | ) qpss              | ) qpac                    |      |

| Transient Analysis                         |        |                             |                     |                           |      |

| Stop Time 390u                             |        |                             |                     |                           |      |

| Accuracy Defaults (empreset)               |        |                             |                     |                           |      |

| Enabled Options                            |        |                             |                     |                           |      |

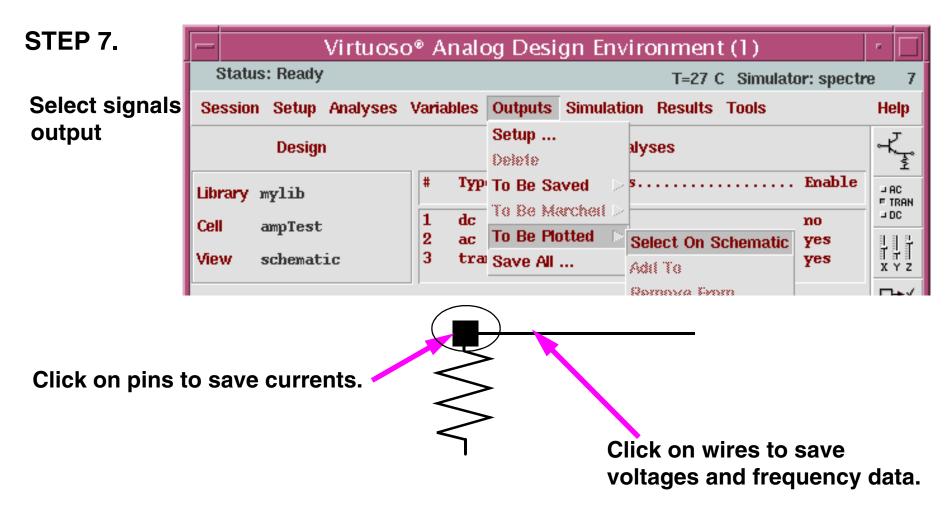

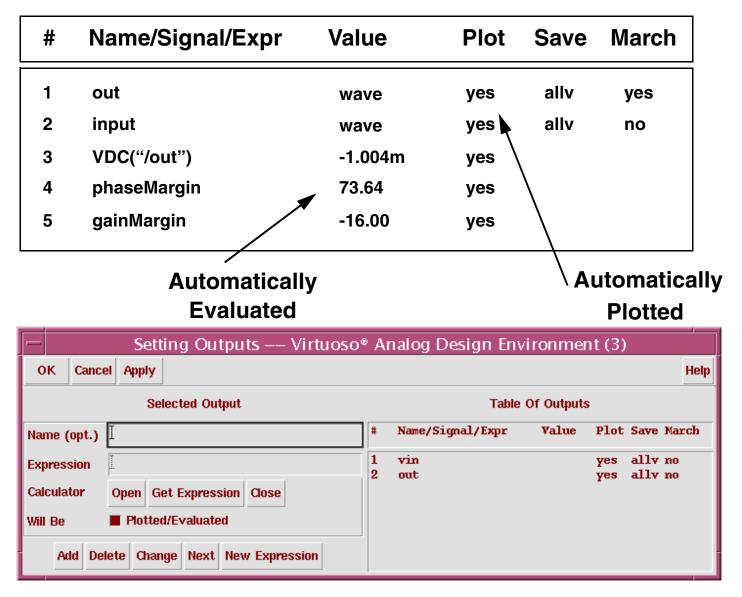

### **Saving Outputs for Plotting**

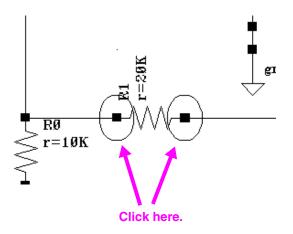

Select the nodes that will be plotted automatically when the simulation is complete. You will select your nodes in the *peakDetectv* schematic.

- 1. If the *peakDetectv* schematic is visible, proceed to Step 4.

- 2. If the *peakTestv* schematic is visible instead of the *peakDetectv* schematic, select the *peakDetectv* block and execute **Design—Hierarchy—Descend Edit**.

**Tip:** You can also press **E** (Shift E).

3. In the Descend form that appears, set the View Name to **schematic**, and click **OK**.

The *peakDetectv* schematic appears.

4. Execute Outputs—To Be Plotted—Select On Schematic.

Follow the prompts at the bottom of the schematic window and click on the wire or wires connected to the pins labeled *vinput*, *vcap*, and *vcontrol*. The nodes will highlight with unique colors. 5. With your cursor in the schematic window, press Esc.

Note the updates in the Outputs section of the Simulation window. The signal *vcontrol* has the name *I54/vcontrol*.

Do you know why?

Does your simulation window look similar to this?

| - Virtuoso             | o® Analog Design Environment (2)                 | •            |  |

|------------------------|--------------------------------------------------|--------------|--|

| Status: Ready          | T=27 C Simulator: spectre                        | 18           |  |

| Session Setup Analyses | Variables Outputs Simulation Results Tools       | Help         |  |

| Design                 | Analyses                                         | Ļ            |  |

| Library training       | # Type Arguments Enable                          |              |  |

| Cell peakTesty         | 1 tran 0 390u yes                                | ⊐ DC         |  |

| View schematic         |                                                  | III<br>XYZ   |  |

| Design Variables       | Outputs                                          | <b>⊡</b> ≣∵́ |  |

| # Name Value           | # Name/Signal/Expr Value Plot Save March         | <u></u>      |  |

| 1 cload 500p<br>2 VL 0 | 1 vinput yes allv no<br>2 vcap yes allv no       | <u> </u>     |  |

| 3 VH 5                 | 2 vcap yes allv no<br>3 I54/vcontrol yes allv no | 8            |  |

| 4 pul 40u<br>5 per 50u |                                                  |              |  |

| >                      | Plotting mode: Replace                           | $\sim$       |  |

| >                      |                                                  | L            |  |

Note: At this point, you can save these environment settings using the Session—Save State command, enter state1 in the *Save As* field then click **OK**. This will allow you to reload these settings next time you work with this schematic.

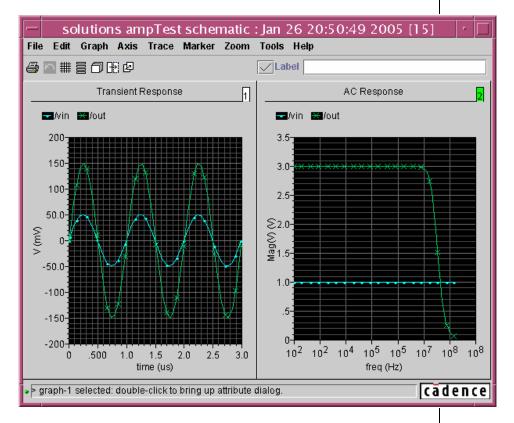

#### **Running the Simulation**

You will run the simulation and view the results. You will not need to generate and view a netlist before running simulation. If you choose to view a netlist, you can use the **Simulation—Netlist—Create** command.

1. Execute **Simulation—Netlist and Run** to start the simulation or click the **Netlist and Run** icon in the Simulation window.

The simulation starts, and a separate window appears and prints the simulation status as it runs. If there are errors in the setup, you will receive messages in this window directing you to take appropriate action. See if you can debug the errors, or check with the instructor.

You might try creating a netlist and then clicking the **Run** icon to run the simulation, after you have corrected your errors.

When the simulation completes, the Transient analysis results plot automatically.

training peakTestv schematic : Oct 10 18:38:20 2004 [6] File Edit Graph Axis Trace Marker Zoom Tools Help 😂 📉 # 🗏 🗍 🖽 Ø Label Transient Response Avinput 💥 Асар /I54/vcontrol 5-S 3-50.0 100 150 200 250 300 350 400 time (us) cadence graph-1.trace0:/vinput

Does your Waveform Window look like this?

Note the following:

- The load capacitor stores the peak value of the input voltage as it is being charged (signal *vcap*).

- The *vcontrol* signal is applied to the gate of the NMOS device that discharges the load capacitor. It turns the transistor on or off.

- The pulse width of the *vcontrol* signal determines how much of the capacitor charge is dissipated.

### Preparing for the Next Lab

- 1. In the Simulation window, execute Session—Quit.

- 2. In the schematic window, execute **Window—Close**. Click **No** in the Save Changes form if it comes up.

- 3. In the window that was started by the Simulation environment, execute **File**—**Close Window**.

Now that you have simulated a high-level, block description of your design by using AHDL, you will begin to build the schematics of each block in your design. The schematic-level blocks that you build will be used in several different designs in your labs.

In the next lab, you will start by creating a library, and then by building a schematic for the opamp that you simulated in this lab.

Top-Down System Modeling

# **Schematic Entry**

Module 2

February 10, 2005

# **Topics in this Module**

- The schematic capture flow

- Creating a schematic view

- Contents of a schematic

- Adding component instances

- Adding pins

- Adding wires

- Editing object properties

- Using Accelerator keys (also known as bindkeys) and schematic window icons

- Checking the schematic for errors

- Symbol generation and editing

- Using a design hierarchy

# **Terms and Definitions**

| library                         | A set of design directories that includes 'cells' and 'cellviews'.       |

|---------------------------------|--------------------------------------------------------------------------|

| Library Manage                  | • A Cadence tool that allows user to browse and edit a design library.   |

| Virtuoso<br>Schematic<br>Editor | Schematic editor and symbol generation tool in DFII.                     |

| cell                            | A basic unit of a design hierarchy described by cell views.              |

| cell view                       | A specific view of a cell that includes schematic, symbol or layout.     |

| instance                        | A uniquely named placement of a symbol onto a schematic.                 |

| pin                             | A connection point on a schematic and symbol used for accessing signals. |

| bindkey                         | A predefined key on the keyboard that invokes a preselected command.     |

# **Schematic Entry Flow**

Schematic Entry

Perform the following steps when creating a schematic:

- 1. Open the design. Use the CIW or Library Manager tool.

- 2. Add component instances by placing cellviews from libraries.

- 3. Add or modify component parameters.

- 4. Add pins to indicate connections outside of this schematic.

- 5. Connect the components and pins.

Use wires to do this. This step also includes giving meaningful names to signals in the design.

- 6. Check the design to ensure that it is correct.

- 7. Save the design.

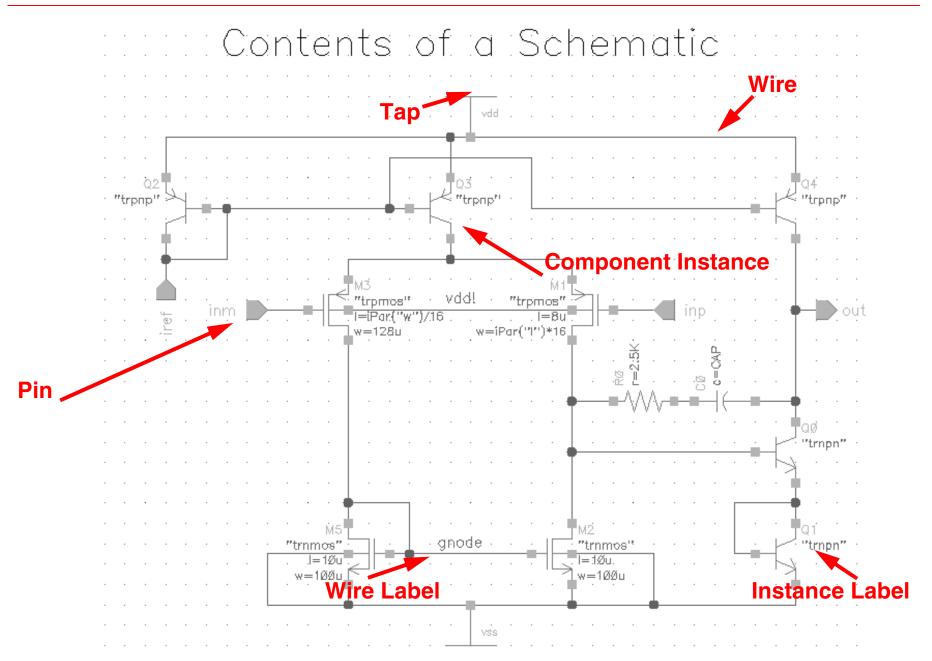

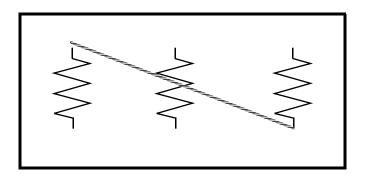

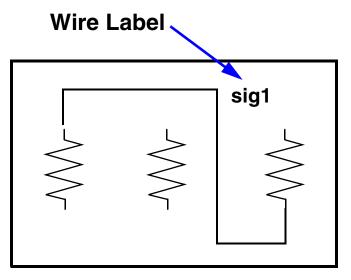

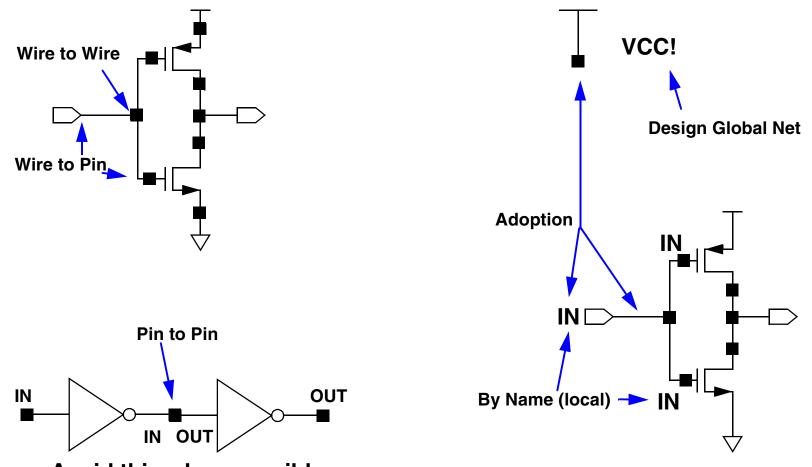

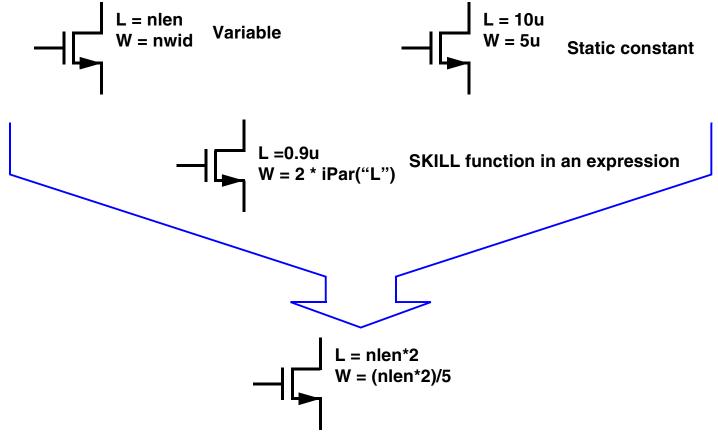

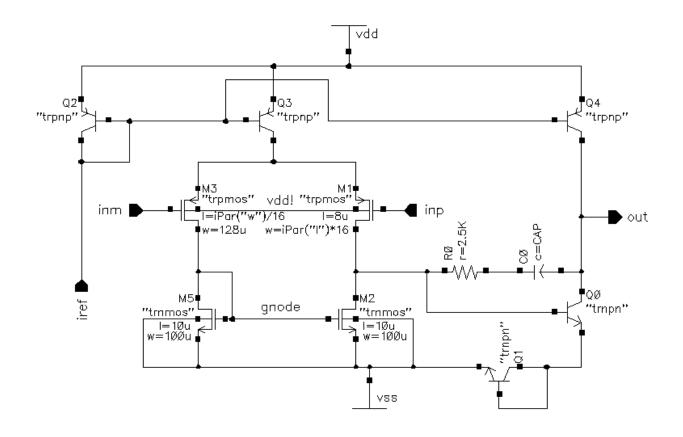

### **Contents of a Schematic**

#### Schematic Entry

- Component instances represent instantiations of other cellviews in this cellview.

- Instance labels display component information in the design entry window.

- Pins can be inputs and outputs of a schematic or connection point when an instance is placed in another cellview.

- Wires can be drawn between pins to connect them.

- Wire labels provide meaningful signal identifiers for simulation results analysis.

- Analog taps and sources can be included directly in the design.

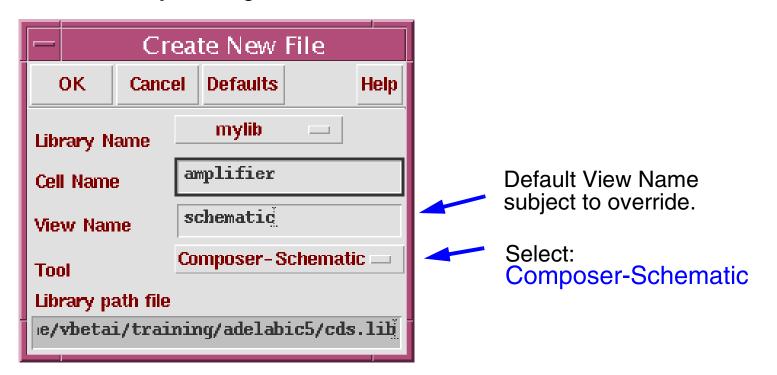

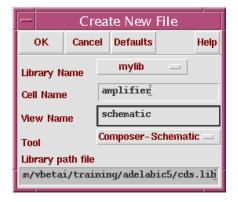

# **Creating a New Cellview**

In the CIW or Library Manager, select File—New—Cellview.

- Specify the Library Name, Cell Name, View Name, and Tool to use. The path to the *cds.lib* file will appear in the form and is not editable.

- Modify the Tool field to create a layout, verilog, symbol, schematic, vhdl, or ahdl view.

For an ADE schematic, select **Composer-Schematic** from the Tool cyclic field

Create a new cell views from the Library Manager or CIW.

Specify the Library Name, Cell Name, View Name, and Tool to use. The path to the *cds.lib* file will appear in the form and is not editable.

Modify the Tool field to create a *layout*, *verilog*, *symbol*, *schematic*, *vhdl*, or *ahdl* view. For a schematic, use *Composer-Schematic*. This will automatically enter *schematic* into the View Name text field.

Although *schematic* is automatically entered into the View Name text field by default, you have the option to name the view anything you want. For example, the View Name may be altered to *schem1*, and the process repeated for *schem2*. As such, there are two or more schematic views for the same cell name. This allows parallel circuit designs within the same cell name. A common symbol for both schematics is then used within the hierarchy, until the final schematic is selected. This feature is useful in exploratory designs where the final circuit topology has not yet been finalized.

### **Adding Component Instances**

Select **Add—Instance** or press the **i** key to display the Add Instance form.

- Attach multipliers to values. Enter 1k (not 1 k) so that k is not mistaken as a variable.

- Parameter units, such as ohms, are implicit.

|                                           |                                                                                         | Ad                                                                                                                                       | d Insta                                                                                                                                             | ince                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                 |

|-------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hide                                      | Cancel                                                                                  | Defaults                                                                                                                                 |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                          | Help                                                                                                                                                                                                                            |

| Library<br>Cell<br>View<br>Names<br>Array | reš<br>symbol<br>R[                                                                     |                                                                                                                                          | Y.                                                                                                                                                  | Columns                                                                                                                                                                                                                                                                                                                                                  | Browse                                                                                                                                                                                                                          |

| Rotat                                     | e                                                                                       | Sid                                                                                                                                      | leways                                                                                                                                              | L                                                                                                                                                                                                                                                                                                                                                        | lpside Down                                                                                                                                                                                                                     |

|                                           |                                                                                         |                                                                                                                                          |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                 |